### L9779WD-SPI

### Multifunction IC for engine management system

#### Datasheet - production data

Protected low-side (high current) - OUT5, 6, 7 Protected low-side (low current) OUT20 IGBT pre-drivers (IGN1 to 4) with parallel input Parallel input IN1 to IN7 to drive OUT1 to OUT7 Configurable power stages CPS HiQUAD-64 - Stepper motor driver/ high-side - low-side (OUTA to D) Thermal warning and shutdown Serial interface - SPI 16-bit frame Features ISO9141 interface (K-Line) 5 V logic regulator High speed CAN transceiver 3.3 V logic regulator VDA 2.0 compliance with 3 level Watchdog 5 V tracking sensor supply Package: HiQUAD-64 Smart reset function Description Power latch with Secure Engine Off (SEO) functionality, to safely complete driver switch

The L9779WD-SPI is an integrated circuit designed for automotive environment and implemented in BCD6S technology.

It is conceived to provide all basic functions for standard engine management control units.

It is assembled in the HiQUAD-64 power package.

#### Table 1. Device summary

|                | Table II Berlee callinary |               |

|----------------|---------------------------|---------------|

| Order code     | Package E                 | Packing       |

| L9779WD-SPI    | HiQUAD-64                 | Tray          |

| L9779WD-SPI-TR | HiQUAD-64                 | Tape and Reel |

off procedure

OUT1 to 4

Flying wheel interface function (VRS) with

adaptive time and amplitude control

Protected low-side (injector drivers)

Protected low-side relay driver

OUT13 to 18, MRD

DocID027721 Rev 2

This is information on a product in full production.

### Contents

| 1 | Detailed features description9 |                                                     |      |  |  |

|---|--------------------------------|-----------------------------------------------------|------|--|--|

| 2 | Block                          | Block diagram                                       |      |  |  |

| 3 | Pins                           | description                                         | 12   |  |  |

| 4 | Appli                          | cation schematic                                    | 16   |  |  |

| 5 | Abso                           | lute maximum ratings                                | 17   |  |  |

|   | 5.1                            | ESD protection                                      | 18   |  |  |

|   | 5.2                            | Latch-up test                                       | 19   |  |  |

|   | 5.3                            | Temperature ranges and thermal data                 | 19   |  |  |

|   | 5.4                            | Operating range                                     |      |  |  |

|   |                                | 5.4.1 Low battery                                   | . 19 |  |  |

|   |                                | 5.4.2 Normal battery                                | . 19 |  |  |

|   |                                | 5.4.3 High battery                                  |      |  |  |

|   |                                | 5.4.4 Load dump                                     | . 19 |  |  |

| 6 | Funct                          | tional description                                  | 20   |  |  |

|   | 6.1                            | Ignition switch, main relay, battery pin            |      |  |  |

|   | 6.2                            | Power-up/down management unit                       |      |  |  |

|   | 1                              | 6.2.1 Power-up sequence                             |      |  |  |

|   |                                | 6.2.2 Power-down sequence                           | . 23 |  |  |

|   | 6.3                            | Smart reset circuit                                 | 29   |  |  |

|   |                                | 6.3.1 Smart reset circuit functionality description | . 29 |  |  |

|   | 6.4                            | Th <mark>ermal shut</mark> down                     | 33   |  |  |

|   | 6.5                            | Voltage regulators                                  | 34   |  |  |

|   | 6.6                            |                                                     | 40   |  |  |

|   | 6.7                            | Main relay driver                                   | 44   |  |  |

|   |                                | 6.7.1 Main relay driver functionality description   | . 44 |  |  |

|   |                                | 6.7.2 MRD scenarios                                 | . 45 |  |  |

|   | 6.8                            | Low-side switch function (LSa, LSb, LSd)            | 50   |  |  |

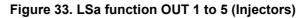

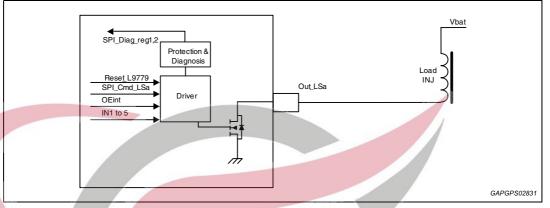

|   |                                | 6.8.1 LSa function OUT 1 to 5 (Injectors)           | 50   |  |  |

2/141

DocID027721 Rev 2

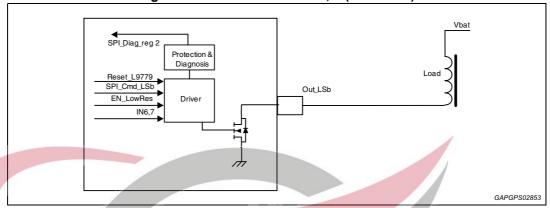

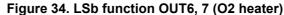

|                                       | 6.8.2    | LSb function OUT6, 7 (O2 heater)                                               | 53    |

|---------------------------------------|----------|--------------------------------------------------------------------------------|-------|

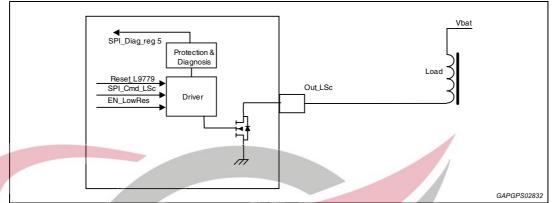

|                                       | 6.8.3    | LSc function OUT20 (low current drivers)                                       | 55    |

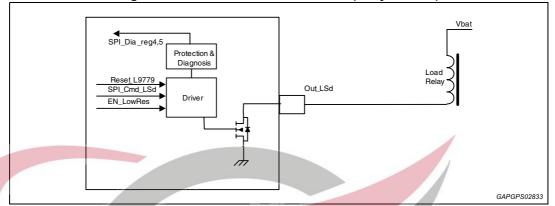

|                                       | 6.8.4    | LSd function OUT13 to 18 (relay drivers)                                       | 57    |

| 6.9                                   | LSa, LS  | Sb, LSc, LSd diagnosis                                                         | . 62  |

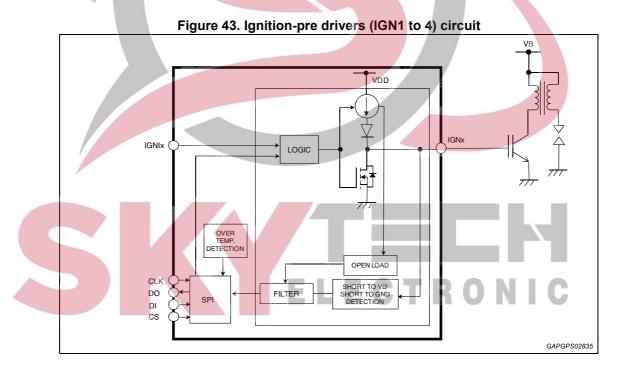

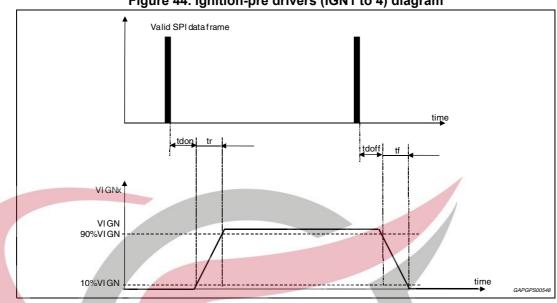

| 6.10 Ignition pre-drivers (IGN1 to 4) |          |                                                                                | . 64  |

|                                       | 6.10.1   | Ignition pre-drivers functionality description                                 | 65    |

|                                       | 6.10.2   | Ignition pre-driver diagnosis                                                  | 66    |

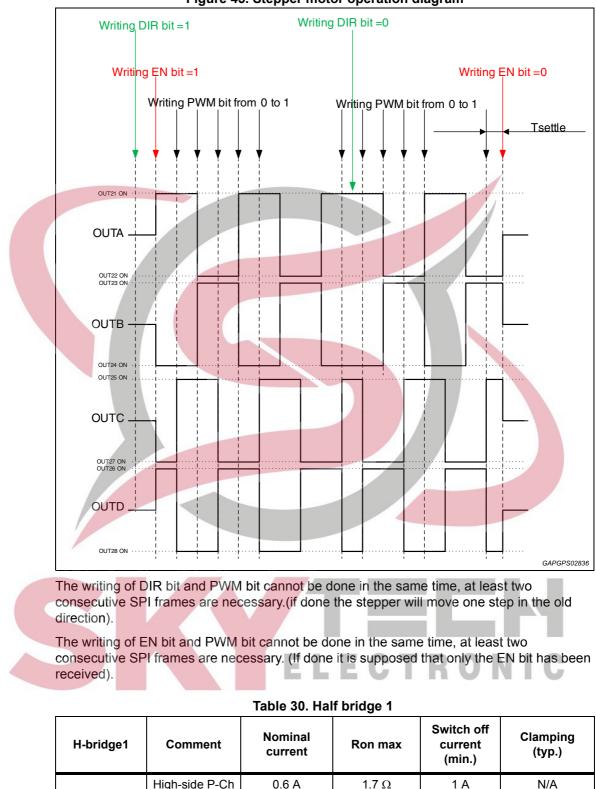

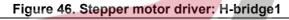

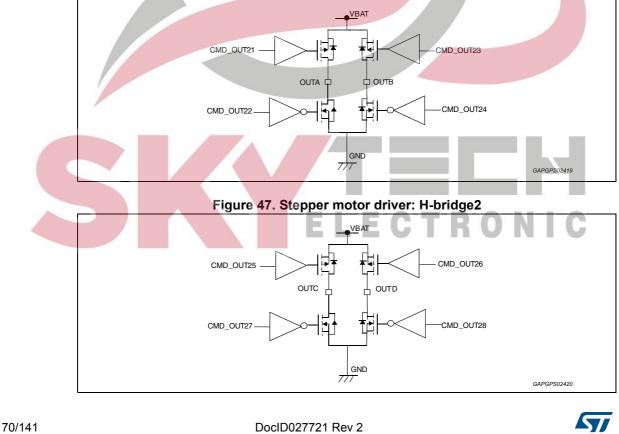

| 6.11                                  | Configu  | urable power stages (CPS) (OUTA to OUTD)                                       | . 67  |

|                                       | 6.11.1   | Configurable power stages functionality description                            |       |

|                                       | 6.11.2   | Diagnosis of configurable power stages (CPS)                                   |       |

|                                       | 6.11.3   | Diagnosis of CPS [OUTA to OUTD] when configured as H-bridges                   | 71    |

|                                       | 6.11.4   | Diagnosis of CPS OUTA, B, C, D when configured as single low side power stages |       |

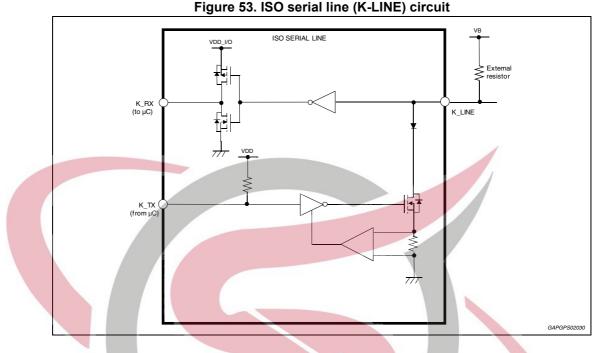

| 6.12                                  | ISO se   | rial line (K-LINE)                                                             | . 80  |

|                                       | 6.12.1   | ISO serial line (K-LINE) functionality description                             | 80    |

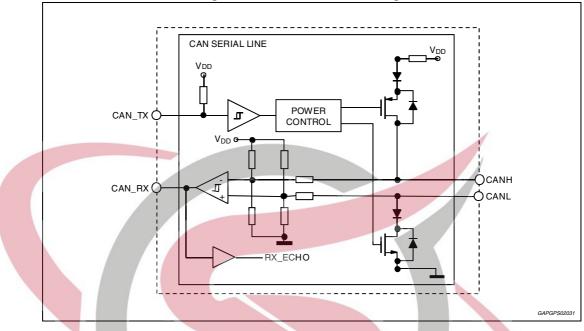

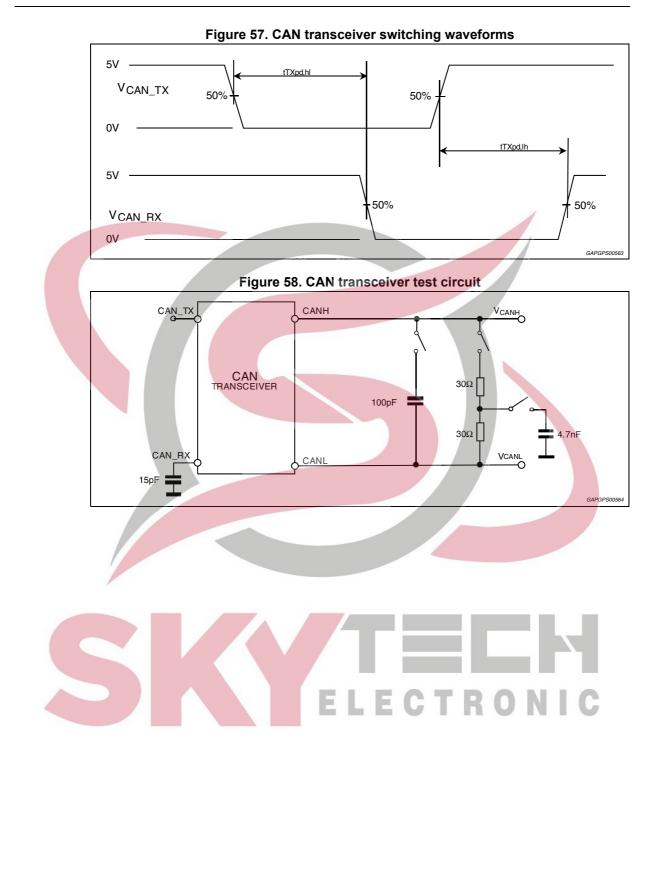

| 6.13                                  | CAN tra  | ansc <mark>eiver</mark>                                                        | . 83  |

|                                       | 6.13.1   | CAN transceiver functionality description                                      | 83    |

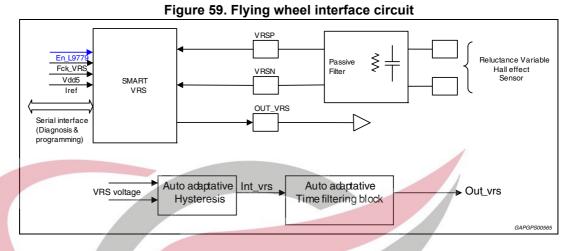

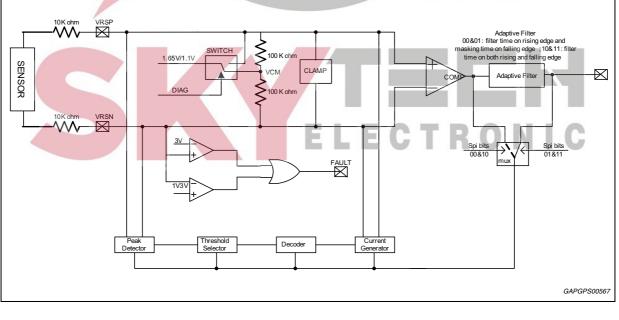

| 6.14                                  | Flying   | wheel interface function                                                       | . 88  |

|                                       | 6.14.1   | Flying wheel interface functionality description                               | 88    |

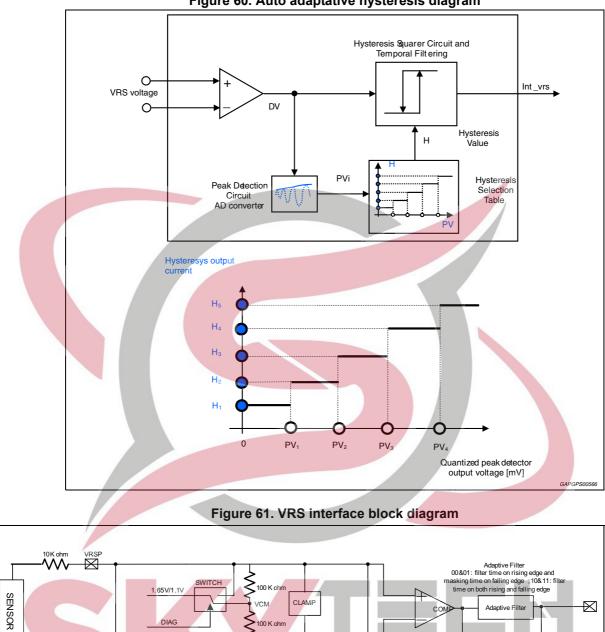

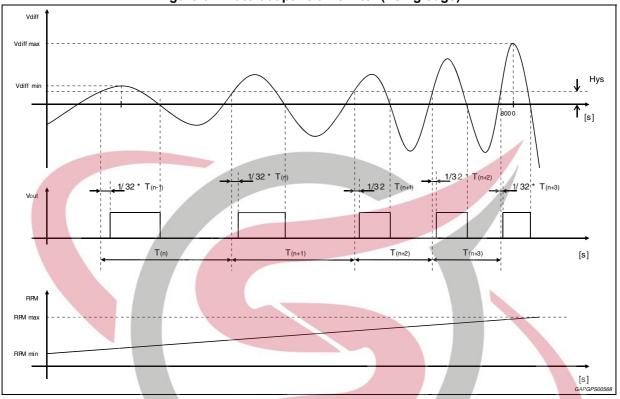

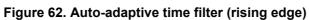

|                                       | 6.14.2   | Auto-adaptive sensor filter                                                    |       |

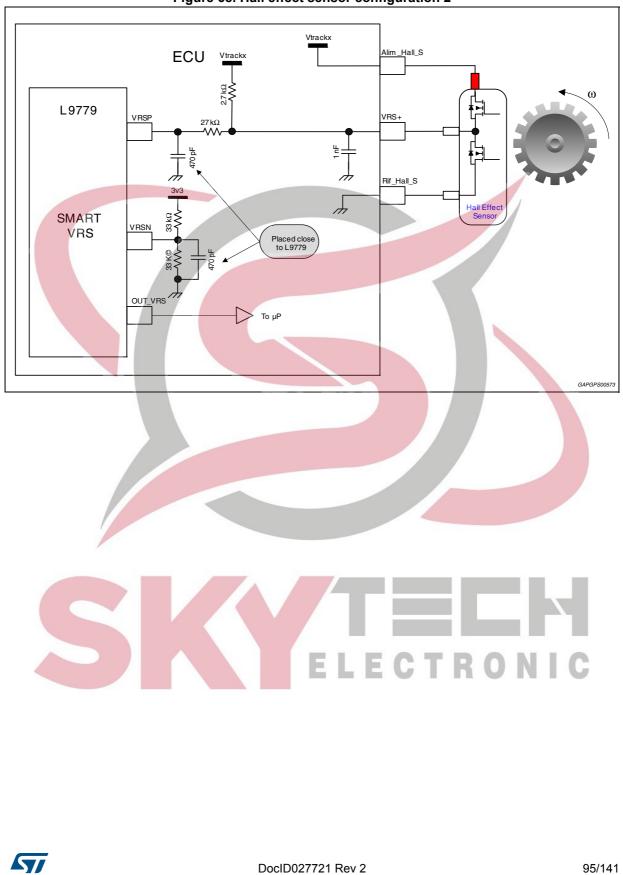

|                                       | 6.14.3   | Application circuits                                                           | 93    |

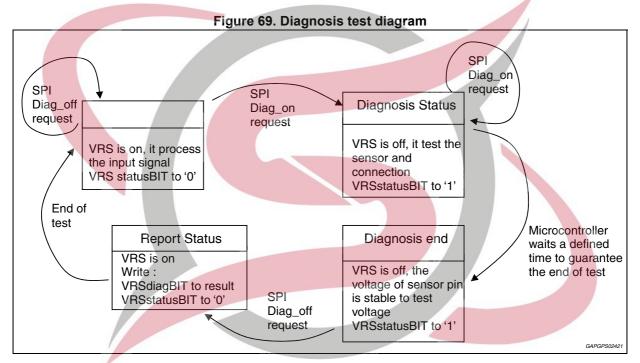

|                                       | 6.14.4   | Diagnosis test                                                                 | 96    |

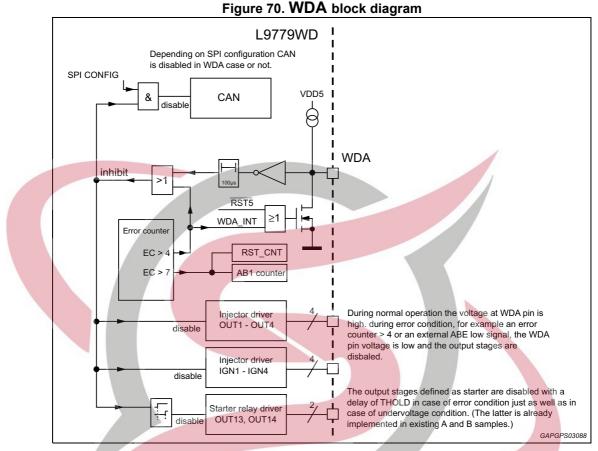

| 6.15                                  | Monito   | ring module (watchdog)                                                         | . 98  |

|                                       | 6.15.1   | WDA - Watchdog (algorithmic)                                                   | 98    |

|                                       | 6.15.2   | Monitoring module - WDA Functionality                                          | 99    |

| 6.16                                  | Serial i | nterface                                                                       | 108   |

|                                       | 6.16.1   | SPI interface                                                                  | . 108 |

|                                       | 6.16.2   | SPI protocol                                                                   | . 108 |

|                                       | 6.16.3   | SPI registers                                                                  | . 110 |

|                                       |          | CONFIG_REG1                                                                    |       |

|                                       |          | CONFIG_REG2                                                                    |       |

|                                       |          | CONFIG_REG3<br>CONFIG_REG4                                                     |       |

|                                       |          | CONFIG_REG5                                                                    |       |

|                                       |          | CONFIG_REG6                                                                    |       |

|                                       |          | CONFIG_REG7                                                                    | 119   |

|                                       |          | WD_ANSW/WDA RESP/CONFIG_REG8                                                   | 120   |

|                                       |          |                                                                                |       |

|   |        | CONFIG_REG9/SPI RESPTIME12                | 20        |

|---|--------|-------------------------------------------|-----------|

|   |        | CONFIG_REG10 (CPS Configuration register) | 21        |

|   |        | IDENT_REG/DIA_REG[1:5]12                  | 21        |

|   |        | DIA_REG612                                | 24        |

|   |        | DIA_REG712                                | 25        |

|   |        | DIA_REG812                                | 26        |

|   |        | DIA_REG912                                | 27        |

|   |        | DIA_REG10                                 | 28        |

|   |        | DIA_REG11                                 | <u>29</u> |

|   |        | DIA_REG12                                 | 30        |

|   |        | DIA_REG13/WDA_RESPTIME13                  | 31        |

|   |        | DIA_REG14/REQULO                          | 31        |

|   |        | DIA_REG15/REQUHI                          | 32        |

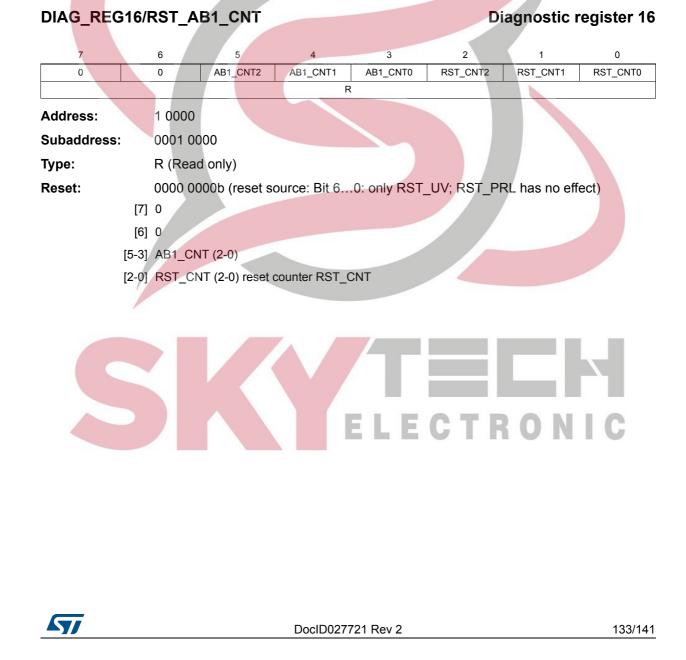

|   |        | DIAG_REG16/RST_AB1_CNT                    | 33        |

|   |        | CONTR_REG1                                | 34        |

|   |        | CONTR_REG2                                | 35        |

|   |        | CONTR_REG3                                | 36        |

|   |        | CONTR_REG4                                | 37        |

|   |        |                                           |           |

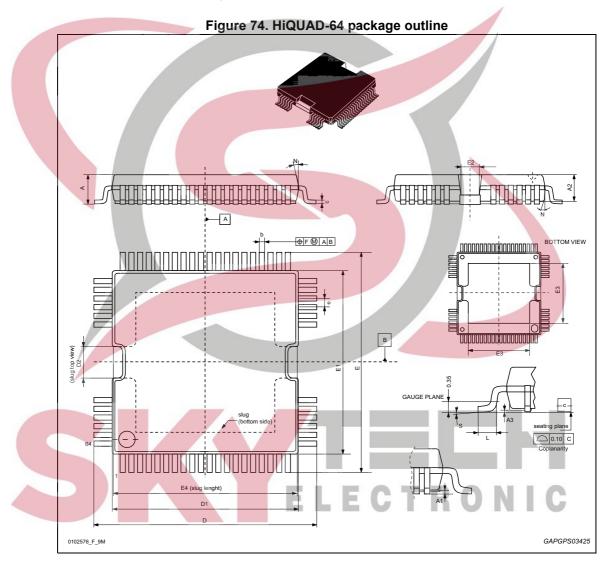

| 7 | Pack   | age information                           | 8         |

|   | 7.1    | HiQUAD-64 package information 13          | 8         |

|   |        |                                           | •         |

| 8 | Rovie  | sion history                              | 0         |

| 0 | ILEVI3 |                                           | U         |

|   |        |                                           |           |

|   |        |                                           |           |

|   |        |                                           |           |

|   |        |                                           |           |

|   |        |                                           |           |

|   |        |                                           |           |

|   |        |                                           |           |

|   |        |                                           |           |

|   |        |                                           |           |

|   |        | ELECTDONIC                                |           |

|   |        |                                           |           |

### List of tables

| Table 1.  | Device summary                                                                      | 1    |  |  |

|-----------|-------------------------------------------------------------------------------------|------|--|--|

| Table 2.  | Pins description                                                                    | . 12 |  |  |

| Table 3.  | Absolute maximum ratings                                                            | . 17 |  |  |

| Table 4.  | ESD protection                                                                      |      |  |  |

| Table 5.  | Temperature ranges and thermal data                                                 | . 19 |  |  |

| Table 6.  | Operating range                                                                     | . 19 |  |  |

| Table 7.  | KEY_ON pin electrical characteristics                                               | . 28 |  |  |

| Table 8.  | Internal reset                                                                      | . 30 |  |  |

| Table 9.  | RST pin external components required                                                | . 32 |  |  |

| Table 10. | RST pin electrical characteristics                                                  |      |  |  |

| Table 11. | Temperature information                                                             | . 33 |  |  |

| Table 12. | Voltage regulators external components required                                     |      |  |  |

| Table 13. | VB Power supply electrical characteristics                                          | . 37 |  |  |

| Table 14. | Linear 5 V regulator electrical characteristics                                     | . 38 |  |  |

| Table 15. | Linear 3.3 V regulator electrical characteristics                                   |      |  |  |

| Table 16. | 5V tracking sensor supply electrical characteristics                                | . 43 |  |  |

| Table 17. | Main relay driver electrical characteristics                                        | . 45 |  |  |

| Table 18. | LSa electrical characteristics                                                      | . 50 |  |  |

| Table 19. | LSa diagnosis electrical characteristics                                            | . 52 |  |  |

| Table 20. | LSa diagnosis electrical characteristics (OUT 5)                                    | . 52 |  |  |

| Table 21. | LSb electrical characteristics                                                      |      |  |  |

| Table 22. | LSb diagnosis electrical characteristics                                            | . 54 |  |  |

| Table 23. | LSc electrical characteristics                                                      |      |  |  |

| Table 24. | LSc diagnosis electrical characteristics                                            |      |  |  |

| Table 25. | LSd electrical characteristics                                                      | . 57 |  |  |

| Table 26. | LSd diagnosis electrical characteristics                                            | . 58 |  |  |

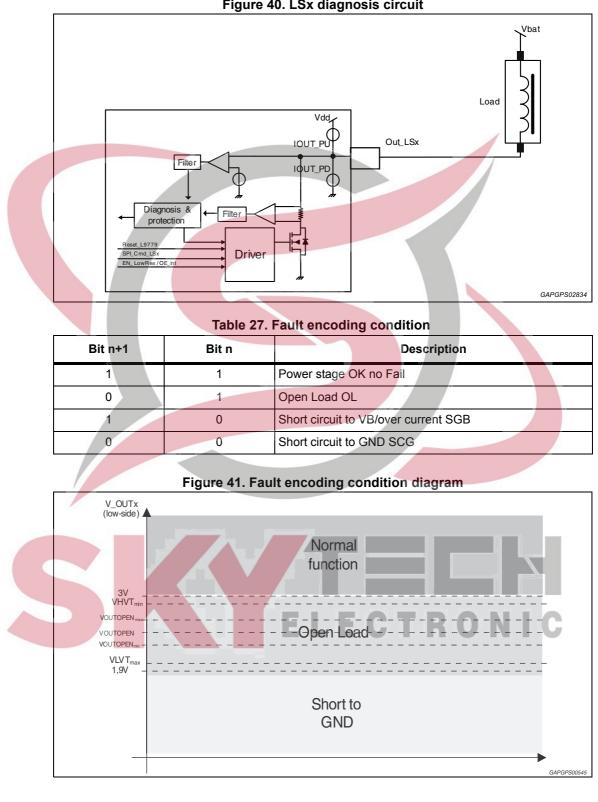

| Table 27. | Fault encoding condition                                                            |      |  |  |

| Table 28. | Ignition pre-drivers electrical characteristics                                     | . 65 |  |  |

| Table 29. | Configuration of the stepper motor                                                  |      |  |  |

| Table 30. | Half bridge 1                                                                       |      |  |  |

| Table 31. | Half bridge 2                                                                       | . 70 |  |  |

| Table 32. | Half bridge 3                                                                       | . 70 |  |  |

| Table 33. | Half bridge 4                                                                       | . 70 |  |  |

| Table 34. | Stepper configuration electrical characteristics                                    | . 75 |  |  |

| Table 35. | Electrical and diagnosis characteristics of OUTA, B, C, D when configured as single |      |  |  |

|           | power stages                                                                        | . 77 |  |  |

| Table 36. | Electrical characteristics of OUTA, B, C, D when configured as single power stages  |      |  |  |

|           | connected in parallel                                                               | . 78 |  |  |

| Table 37. | CPS table single mode parallelism.                                                  | . 79 |  |  |

| Table 38. | Three configurations of CONFIG_REG10 register                                       | . 79 |  |  |

| Table 39. | ISO serial line (K-LINE) functionality electrical characteristic                    | . 81 |  |  |

| Table 40. | CAN transceiver electrical characteristics.                                         |      |  |  |

| Table 41. | CAN transceiver timing characteristics                                              |      |  |  |

| Table 42. | Pick voltage detector precision                                                     |      |  |  |

| Table 43. | Hysteresis threshold precision                                                      |      |  |  |

| Table 44. | SPI command possible configuration of different option of VRS function.             |      |  |  |

| Table 45. | VRs typical characteristics                                                         |      |  |  |

| Table 46. | Diagnosis test electrical characteristics                                           |      |  |  |

|           | -                                                                                   |      |  |  |

DocID027721 Rev 2

| Table 47. | WDA_INT electrical characteristics.                               |     |

|-----------|-------------------------------------------------------------------|-----|

| Table 48. | Error counter.                                                    | 102 |

| Table 49. | State for <init_wdr> = 1</init_wdr>                               | 103 |

| Table 50. | Reset-behaviour of <wda_int>, AB1 and <wd_rst></wd_rst></wda_int> | 104 |

| Table 51. | Expected responses                                                | 105 |

| Table 52. | Reset behaviour                                                   | 106 |

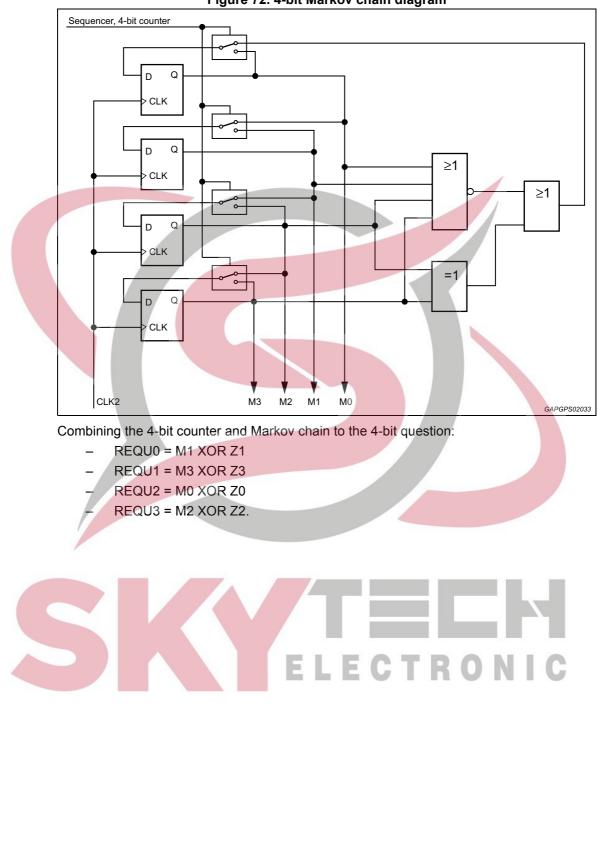

| Table 53. | Timing characteristics                                            | 109 |

| Table 54. | Electrical characteristics                                        |     |

| Table 55. | SPI registers                                                     | 110 |

| Table 56. | CLOCK_UNLOCK_SW_RST                                               | 112 |

| Table 57. | START_REACT                                                       | 112 |

| Table 58. | HiQUAD-64 package mechanical data                                 | 139 |

| Table 59. | Document revision history                                         |     |

### List of figures

| Figure 1.  | Block diagram                                                                    | . 11 |

|------------|----------------------------------------------------------------------------------|------|

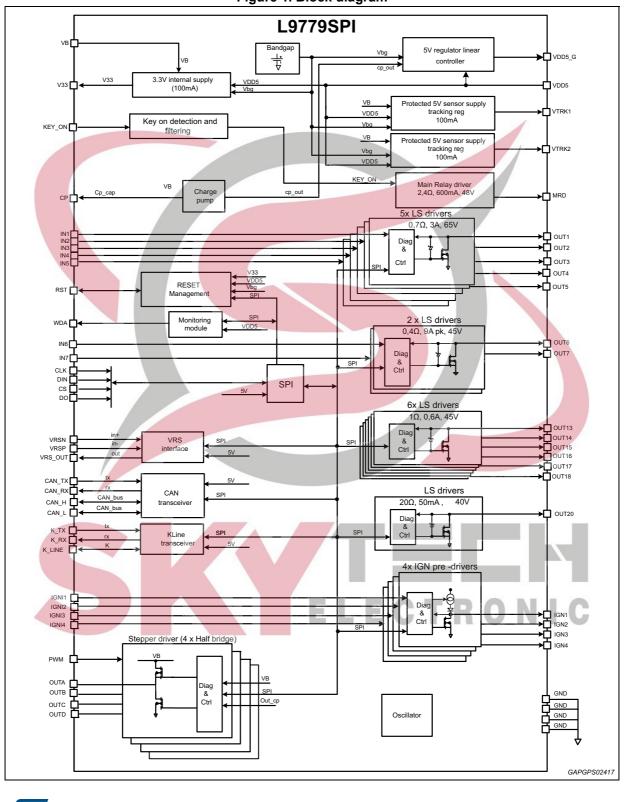

| Figure 2.  | Pins connection diagram (top view)                                               | . 12 |

| Figure 3.  | Application schematic                                                            | . 16 |

| Figure 4.  | Configuration supplied by VB                                                     |      |

| Figure 5.  | Power-up/down management unit                                                    | . 21 |

| Figure 6.  | Non-permanent supply power-up sequence                                           |      |

| Figure 7.  | Permanent supply power-up sequence                                               | . 22 |

| Figure 8.  | Power-down sequence without power latch mode                                     |      |

| Figure 9.  | Power-down sequence without power latch mode and PSOFF = 1                       | . 25 |

| Figure 10. | Power-down sequence with power latch mode                                        | . 26 |

| Figure 11. | Power-down sequence with power latch mode and KEY_ON toggle                      |      |

| Figure 12. | KEY_ON voltage vs. status diagram                                                |      |

| Figure 13. | Smart reset circuit                                                              |      |

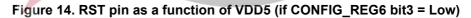

| Figure 14. | RST pin as a function of VDD5 (if CONFIG_REG6 bit3 = Low)                        |      |

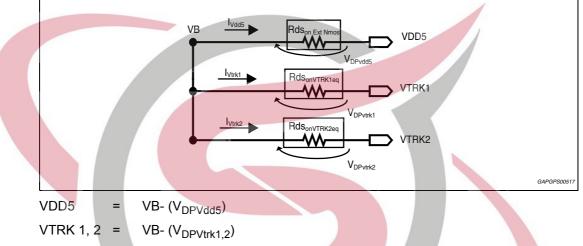

| Figure 15. | Structure regulators diagram                                                     |      |

| Figure 16. | Graphic representation of the calculation method                                 |      |

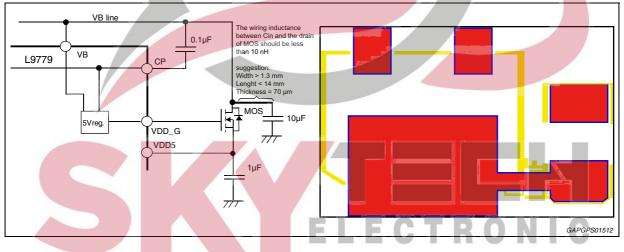

| Figure 17. | Circuit and PCB layout suggested                                                 |      |

| Figure 18. | VB overvoltage diagram                                                           |      |

| Figure 19. | VDD5 overvoltage diagram.                                                        |      |

| Figure 20. | VDD5 vs battery: ramp-up diagram                                                 |      |

| Figure 21. | VDD5 vs battery (ramp-down diagram)                                              |      |

| Figure 22. | Main relay driver controlled by L9779WD-SPI                                      |      |

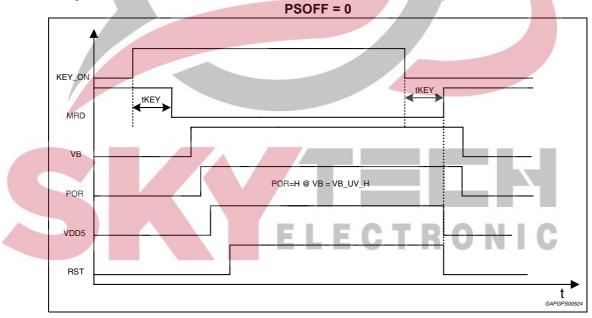

| Figure 23. | Scenario 1a: Standard on/off MRD driver with NO power latch mode bit PSOFF = 0   |      |

| Figure 24. | Scenario 1b: Standard on/off MRD driver with NO power latch mode bit PSOFF = 1   |      |

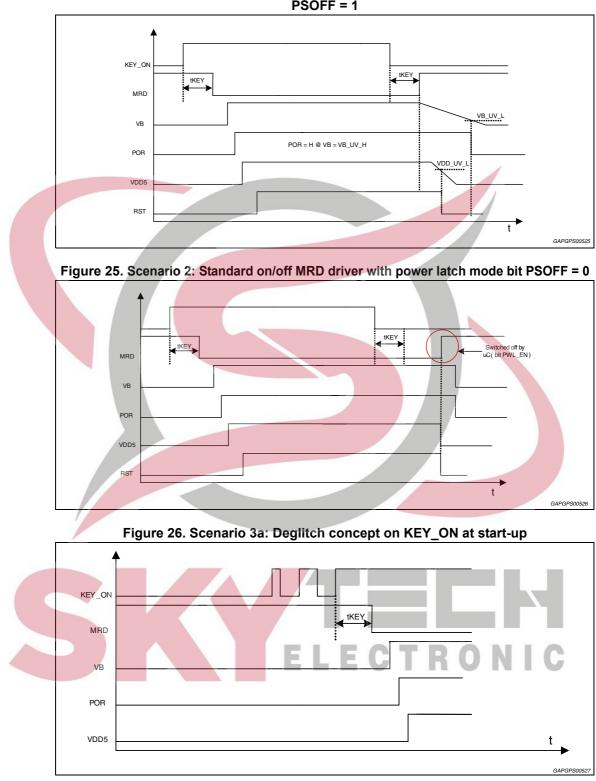

| Figure 25. | Scenario 2: Standard on/off MRD driver with power latch mode bit PSOFF = 0       |      |

| Figure 26. | Scenario 3a: Deglitch concept on KEY_ON at start-up                              |      |

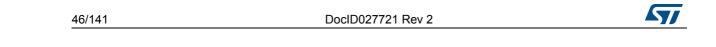

| Figure 27. | Scenario 3b: Deglitch concept on KEY_ON during ON phase                          |      |

| Figure 28. | Scenario 4: Non standard on, KEY_ON removed before VB present                    |      |

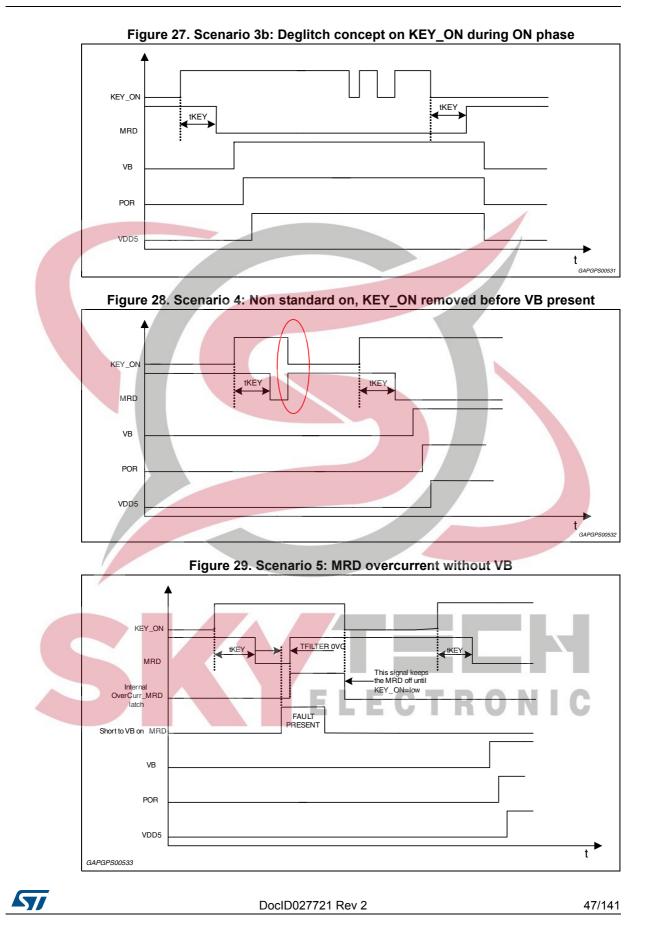

| Figure 29. | Scenario 5: MRD overcurrent without VB                                           |      |

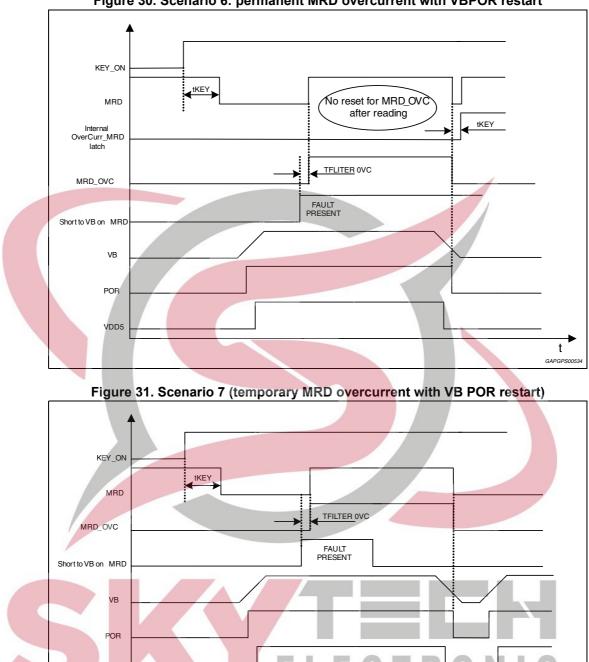

| Figure 30. | Scenario 6: permanent MRD overcurrent with VBPOR restart                         | . 48 |

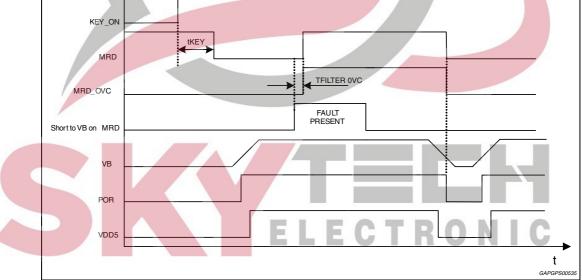

| Figure 31. | Scenario 7 (temporary MRD overcurrent with VB POR restart)                       |      |

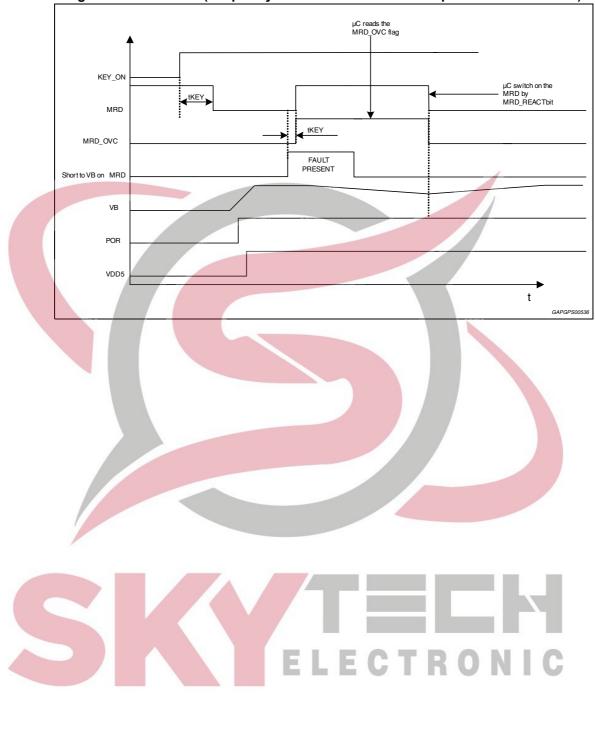

| Figure 32. | Scenario 8 (temporary MRD overcurrent with VB µC commands restart)               |      |

| Figure 33. | LSa function OUT 1 to 5 (Injectors)                                              |      |

| Figure 34. | LSb function OUT6, 7 (O2 heater)                                                 |      |

| Figure 35. | LSc function OUT20 (low current drivers)                                         | . 55 |

| Figure 36. | LSd function OUT13 to 18 (relay drivers)                                         |      |

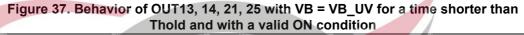

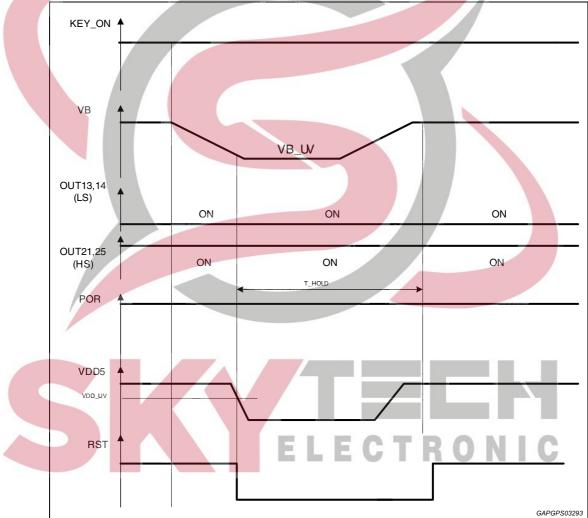

| Figure 37. | Behavior of OUT13, 14, 21, 25 with VB = VB_UV for a time shorter than Thold and  |      |

| J          |                                                                                  | . 59 |

| Figure 38. | with a valid ON condition                                                        |      |

|            |                                                                                  | . 60 |

| Figure 39. | Behavior of OUT13, 14, 21, 25 with VB that drops lower than POR threshold during |      |

| U          | cranking                                                                         | . 61 |

| Figure 40. | LSx diagnosis circuit.                                                           |      |

| Figure 41. | Fault encoding condition diagram                                                 |      |

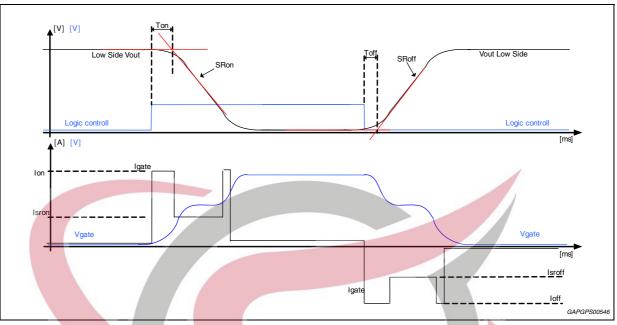

| Figure 42. | LSx ON/OFF slew rate control diagram                                             |      |

| Figure 43. | Ignition-pre drivers (IGN1 to 4) circuit.                                        |      |

| Figure 44. | Ignition-pre drivers (IGN1 to 4) diagram                                         |      |

| Figure 45. | Stepper motor operation diagram                                                  |      |

| 0          |                                                                                  |      |

DocID027721 Rev 2

| Figure 46.                | Stepper motor driver: H-bridge1                         |

|---------------------------|---------------------------------------------------------|

| Figure 47.                | Stepper motor driver: H-bridge2                         |

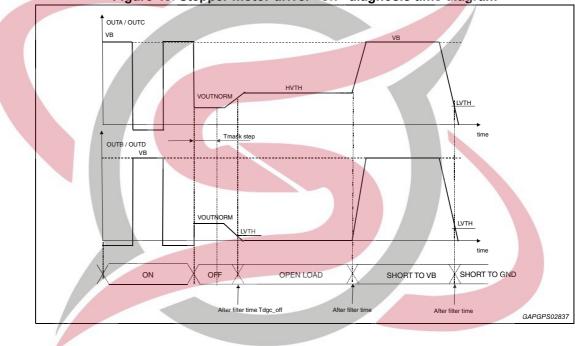

| Figure 48.                | Stepper motor driver "off" diagnosis time diagram       |

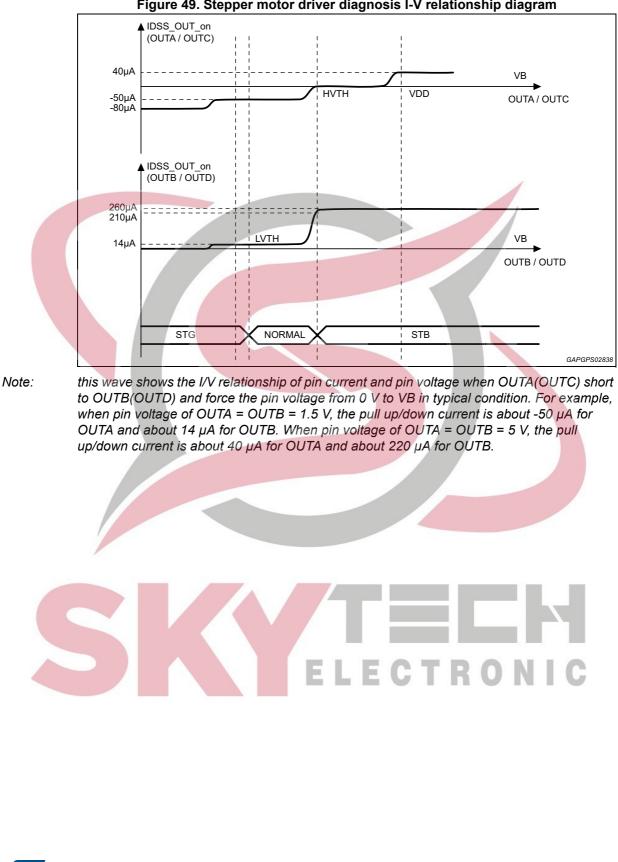

| Figure 49.                | Stepper motor driver diagnosis I-V relationship diagram |

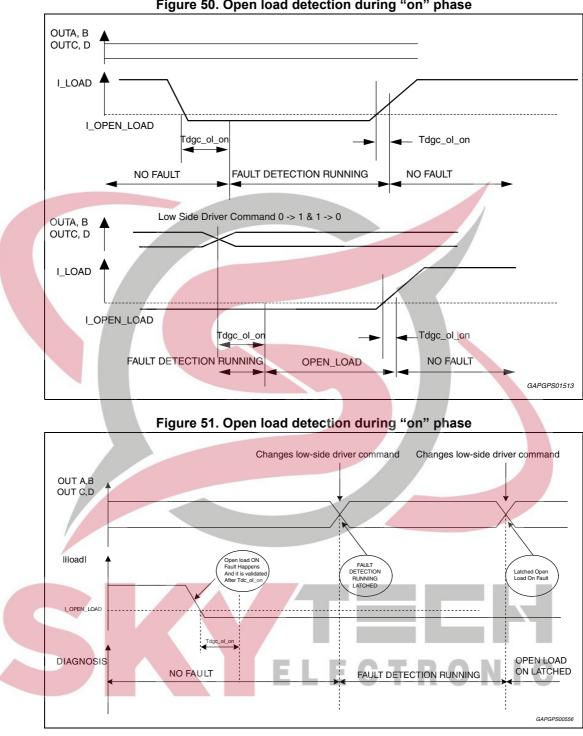

| Figure 50.                | Open load detection during "on" phase                   |

| Figure 51.                | Open load detection during "on" phase                   |

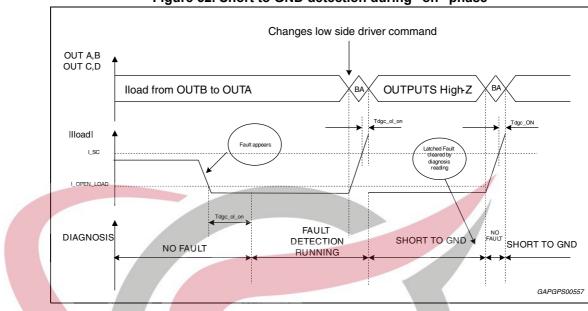

| Figure 52.                | Short to GND detection during "on" phase                |

| Figure 53.                | ISO serial line (K-LINE) circuit                        |

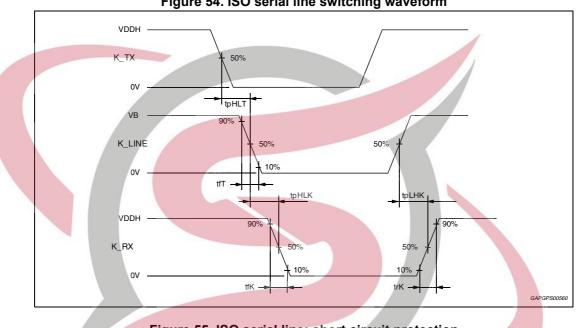

| Figure 54.                | ISO serial line switching waveform                      |

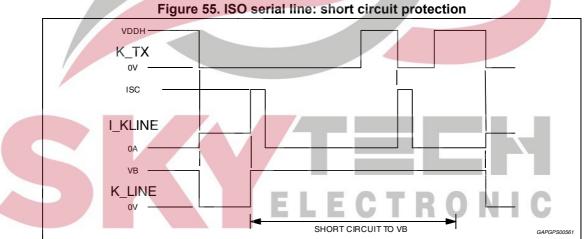

| Figure 55.                | ISO serial line: short circuit protection               |

| Figure 56.                | CAN transceiver diagram                                 |

| Figure 57.                | CAN transceiver switching waveforms                     |

| Figure 58.                | CAN transceiver test circuit                            |

| Figure 59.                | Flying wheel interface circuit                          |

| Figure 60.                | Auto adaptative hysteresis diagram                      |

| Figur <mark>e 61.</mark>  | VRS interface block diagram                             |

| Figur <mark>e 62.</mark>  | Auto-adaptive time filter (rising edge)                 |

| Figur <mark>e 63</mark> . | Adaptive filter function when the SPI bit are 00 or 01  |

| Figure 64.                | Adaptive Filter Function when the SPI bit are 10 or 11  |

| Figure 65.                | Variable reluctance sensor                              |

| Figure 66.                | VRs typical characteristics                             |

| Figure 67.                | Hall effect sensor configuration 1                      |

| Figure 68.                | Hall effect sensor configuration 2                      |

| Figure 69.                | Diagnosis test diagram                                  |

| Figure 70.                | WDA block diagram                                       |

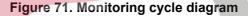

| Figure 71.                | Monitoring cycle diagram                                |

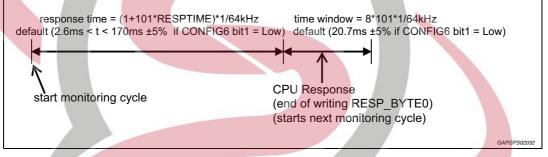

| Figure 72.                | 4-bit Markov chain diagram                              |

| Figure 73.                | Timing characteristics diagram                          |

| Figure 74.                | HiQUAD-64 package outline                               |

|                           |                                                         |

### 1 Detailed features description

- Package

- HiQUAD-64

- 5 V logic regulator

- 5 V precision voltage regulator (± 2%) with external NMOS

- Max current regulated: 400 mA

- Charge pump capacitor at pin CP is used to drive the gate of the external NMOS transistor

- 3.3 V logic regulator

- 3.3 V precision voltage regulator (± 2%) with over-current protection

- Max current regulated: 100 mA

- 5 V tracking sensor supply

- 2 x 5 V tracking sensor supply with protection and diagnosis on SPI

- Short-circuit to Vbat/GND fully protected

- Max current regulated: 2 x 100 mA

- Smart reset

- Main Reset monitoring VB\_UV Logic voltage management and safety control

- Watch dog

- Main reset management 5 V voltage monitoring safety output disable

- SPI controllable query and answer watch dog compliant with VDA2.0 level 3 (enabled by default)

- Power latch

- L9779WD-SPI is switched on by KEY\_ON signal and switched off by logic OR of KEY\_ON signal and SPI bit

- Secure engine off mode (default) switches off the drivers in the following order:

- OUT1 through to OUT4 in 225 ms (typical)

- OUT13 and OUT14 in 600 ms (typical)

- Flying wheel interface function (VRS)

- The VRS is the interface between the microprocessor and the magnetic pick-up or variable reluctance sensor that collects the information coming from the flying wheel

- Adaptive filtering on amplitude and timing adapts better the device response to VRS input switching

- Protected low-side driver

- LSa (OUT1 to 5)

- 4 Ch. serial IN via SPI and parallel IN,  $R_{dson}$  = 0.72 Ohm @150 °C,  $V_{cl}$  = 58 V ±5,  $I_{max}$  = 2.2 A;

- 1 Ch. serial IN via SPI and parallel IN,  $R_{dson}$  = 0.72 Ohm @150°C,  $V_{cl}$  = 58 V ±5,  $I_{max}$  = 3 A;

- LSb (OUT6, 7)

- 2 Ch. serial IN via SPI and parallel IN,  $R_{dson}$  = 0.47 Ohm @150°C,  $V_{cl}$  = 45 V ±5,  $I_{max}$  = 5 A

DocID027721 Rev 2

Full diagnosis on SPI (2 bit for each channel) and voltage slew rate control. When an over current fault occurs, the driver switches off with faster slew rate in order to reduce the power dissipation.

- LSc (OUT20)

- 1 Ch serial IN via SPI, Imax = 50 mA

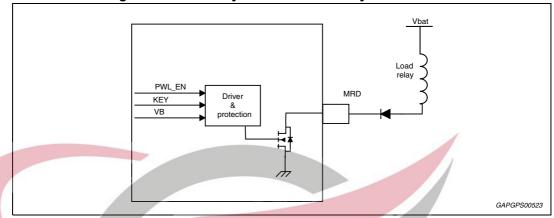

- LSD (OUT13 to 18, MRD)

6 Ch. serial IN via SPI,  $R_{dson}$  = 1.5 Ohm @150 °C,  $V_{cl}$  = 48 V,  $I_{max}$  = 600 mA (2 of them with low battery voltage function);

1 main relay driver  $R_{dson}$  = 2.4 Ohm @150 °C,  $V_{cl}$  = 48 V,  $I_{max}$  = 600 mA

With full diagnosis on SPI (2 bit for each channel) and voltage slew-rate control. When an over current fault occurs, the driver switches off with faster slew rate in order

to reduce the power dissipation.

- Ignition pre-drivers (IGN1 to 4) with parallel input

- 4 x ignition pre-drivers with full diagnostic.

- SPI

- 1 x Stepper motor driver designed for a double winding coil motor, used for engine idle speed control.

The stepper driver is made by 4 independent half bridgeS each one with:

- 1 high-side driver, R<sub>dson</sub> =1.5 Ohm, I<sub>max</sub> = 600 mA

- 1 low-side driver, R<sub>dson</sub> = 1.5 Ohm, I<sub>max</sub> = 600mA

The low-side drivers could be connected in parallel.

Low-side and high-side drivers implement voltage SR control to minimize emission. Two high-side drivers have the low battery voltage function.

- Thermal shutdown

- 1 x Thermal shutdown ( $T_i > 175$  °C = Tsd) if  $T_i > Tsd$ : VTRK1, 2 are turned off.

- 1 x Thermal shutdown ( $T_j > 175$  °C = Tsd) if  $T_j > Tsd$ : OUT1 to 10, OUT13 to 20, OUTA to D, IGN1 to 4 are turned off.

- 1 x Thermal Shutdown ( $T_i > 175 \text{ °C} = \text{Tsd}$ ) if  $T_i > \text{Tsd}$ : V3V3 is turned off.

- 1 x Thermal shutdown ( $T_j > 175 \text{ °C} = Tsd$ ) if  $T_j > Tsd$ : MRD is turned off (if battery present).

There are 5 temperature sensors for OT2 (OUT1..10, OUT13...20, OUT21...28, IGN1...4 are turned off) in different Layout position, they are logically "AND" in case of thermal shutdown.

- ISO9141 interface

- ISO9141 serial interface (K-Line)

- CAN transceiver

The CAN bus transceiver allows the connection of the microcontroller, with CAN controller unit, to a high speed CAN bus with transmission rates up to 1Mbit/s for exchange of data with other ECUs.

DocID027721 Rev 2

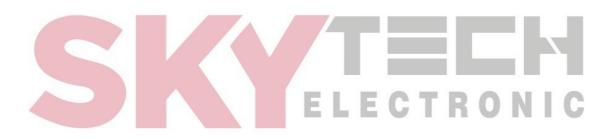

### 2 Block diagram

Figure 1. Block diagram

57

DocID027721 Rev 2

### 3 Pins description

### Table 2. Pins description

| Pin#     | Name   | Function                        | Туре                                             | Polarization/note |

|----------|--------|---------------------------------|--------------------------------------------------|-------------------|

| Supply I | block  |                                 |                                                  |                   |

| 12       | VB     | Battery supply                  | Power supply polarization                        |                   |

| 3        | VDD5   | 5 V output voltage<br>regulator | Power logic output supply                        | UNIC              |

| 2        | VDD_G  | 5 V regulator ext MOS<br>gate   | Analog output                                    | -                 |

| 11       | KEY_ON | Key signal                      | Analog Input protected<br>with<br>20 kΩ resistor | PD 100 kΩ         |

12/141

DocID027721 Rev 2

| Pin#     | Name      | Table 2. Pins descrip<br>Function             | Туре                         | Polarization/note                            |

|----------|-----------|-----------------------------------------------|------------------------------|----------------------------------------------|

| 4        | V3V3      | 3.3 V output voltage<br>regulator             | Power logic output supply    | -                                            |

| 1        | CP        | Charge Pump                                   | Analog Input                 | -                                            |

| 9        | VTRK1     | Sensor1 tracking<br>supply 5V                 | Sensor supply output         | -                                            |

| 10       | VTRK2     | Sensor1 tracking<br>supply 5 V                | Sensor supply output         | -                                            |

| 5        | RST       | Reset output for µP                           | DGT output                   | Open drain $10k\Omega > PU > 1k\Omega^{(1)}$ |

| 38       | WDA       | WDA Interrupt Signal                          | Output: open drain DGT input | -                                            |

| VRS      |           |                                               |                              |                                              |

| 7        | VRSN      | Negative VRS input                            | Analog Input                 | 1.65 V Internal polarization                 |

| 6        | VRSP      | Positive VR <mark>S input</mark>              | Analog Input                 | 1.65 V Internal polarization                 |

| 8        | OUT_VRS   | Digital VRS <mark>output</mark>               | DGT Output                   | Open drain                                   |

| CAN      |           |                                               |                              |                                              |

| 44       | CAN_TX    | Can transceiver<br>input (from TX μP)         | DGT Input                    |                                              |

| 43       | CAN_RX    | Can transceiver<br>output (to RX µP)          | DGT Output                   | -                                            |

| 42       | CAN_H     | Bi-dir protected<br>CAN_H wire                | Analog Input/Output          | -                                            |

| 41       | CAN_L     | Bi-dir protected<br>CAN_L wire                | Analog Input/Output          | -                                            |

| ISO9141  |           |                                               |                              |                                              |

| 47       | K_TX      | ISO9141 logical input                         | DGT Input                    | Ι <sub>Ρu</sub> =20 μΑ                       |

| 45       | K_LINE    | Bi-dir protected K-<br>line wire              | Analog Input/Output          | Open drain                                   |

| 46       | K_RX      | ISO9141 logical<br>output                     | DGT Output                   | Open drain                                   |

| Low side | e drivers |                                               | LEVI-I                       |                                              |

| 60       | OUT1      | Output low-side 1 for<br>R , L Load(Injector) | Power output                 | Open drain                                   |

| 61       | OUT2      | Output low-side 2 for<br>R , L Load(Injector) | Power output                 | Open drain                                   |

| 25       | OUT3      | Output low-side 3 for<br>R , L Load(Injector) | Power output                 | Open drain                                   |

Table 2. Pins description (continued)

| Pin#     | Name                        | Function                                          | Туре         | Polarization/note |  |  |

|----------|-----------------------------|---------------------------------------------------|--------------|-------------------|--|--|

| 28       | OUT4                        | Output low-side 4 for R, L<br>Load(Injector)      | Power output | Open drain        |  |  |

| 26       | PGND3                       | Power GND                                         | PGND1        | -                 |  |  |

| 27       | PGND4                       | Power GND                                         | PGND2        | -                 |  |  |

| 57       | OUT5                        | Output low-side 5 for R , L<br>Load(High current) | Power output | Open drain        |  |  |

| 56       | OUT6                        | Outputlow-side 6 for<br>R , L Load(Heater)        | Power output | Open drain        |  |  |

| 29       | OUT7                        | Output low-side 7 for<br>R , L Load(Heater)       | Power output | Open drain        |  |  |

| 30       | OUT13                       | Output low-side 13 for Relay                      | Power output | Open drain        |  |  |

| 31       | OUT14                       | Output low-side 14 for relay                      | Power output | Open drain        |  |  |

| 54       | OUT15                       | output low-side 15 for relay                      | Power output | Open drain        |  |  |

| 24       | OUT16                       | Output low-s <mark>ide 16 fo</mark> r relay       | Power output | Open drain        |  |  |

| 32       | OUT17                       | Output low-side 17 for relay                      | Power output | Open drain        |  |  |

| 55       | OUT18                       | Output low-side 18 for relay                      | Power output | Open drain        |  |  |

| 58       | PGND3                       | Power GND                                         | PGND3        | -                 |  |  |

| 59       | PGND4                       | Power GND                                         | PGND4        |                   |  |  |

| IGBT pr  | e-driver                    |                                                   |              |                   |  |  |

| 22       | IGN1                        | Output ignition driver 1                          | Power output | -                 |  |  |

| 62       | IGN2                        | Output ignition driver 2                          | Power output | -                 |  |  |

| 63       | IGN3                        | Output ignition driver 3                          | Power output | -                 |  |  |

| 64       | IGN4                        | Output ignition driver 4                          | Power output | -                 |  |  |

| Main rel | ay driver                   |                                                   |              |                   |  |  |

| 23       | MRD                         | Main relay driver                                 | Power output | Open drain        |  |  |

| Low cur  | Low current drivers (50 mA) |                                                   |              |                   |  |  |

| 40       | OUT20                       | Output low-side 20                                | Power output | Open drain        |  |  |

| Parallel | input                       |                                                   | LECTF        | RONIC             |  |  |

| 39       | IN1                         | Parallel input for OUT1                           | DGT Input    | -                 |  |  |

| 48       | IN2                         | Parallel input for OUT2                           | DGT Input    | -                 |  |  |

| 37       | IN3                         | Parallel input for OUT3                           | DGT Input    | -                 |  |  |

| 36       | IN4                         | Parallel input for OUT4                           | DGT Input    | -                 |  |  |

| 35       | IN5                         | Parallel input for OUT5                           | DGT Input    | -                 |  |  |

| 34       | IN6                         | Parallel input for OUT6                           | DGT Input    | -                 |  |  |

| Table 2. | Pins | description | (continued) |

|----------|------|-------------|-------------|

|----------|------|-------------|-------------|

14/141

DocID027721 Rev 2

| Pin#     | Name         | Function                            | Туре         | Polarization/note |

|----------|--------------|-------------------------------------|--------------|-------------------|

| 33       | IN7          | Parallel input for OUT7             | DGT Input    | -                 |

| 49       | PWM<br>(IN8) | PWM input for stepper motor driving | DGT Input    | -                 |

| 19       | IGNI1        | Parallel input for IGN1             | DGT Input    | -                 |

| 18       | IGNI2        | Parallel input for IGN2             | DGT Input    | -                 |

| 15       | IGNI3        | Parallel input for IGN3             | DGT Input    | -                 |

| 14       | IGNI4        | Parallel input for IGN4             | DGT Input    | -                 |

| SPI inte | rface        |                                     |              |                   |

| 51       | SCK          | SPI clock input                     | DGT Input    | -                 |

| 53       | CS           | SPI chip select                     | DGT Input    | -                 |

| 50       | DIN          | SPI data input                      | DGT Input    | -                 |

| 52       | DO           | SPI data output                     | DGT Output   | -                 |

| Stepper  | motor drive  |                                     |              |                   |

| 13       | OUTA         | Stepper                             | Power output | -                 |

| 16       | OUTB         | Stepper                             | Power output | -                 |

| 17       | OUTC         | Stepper                             | Power output | -                 |

| 20       | OUTD         | Stepper                             | Power output | -                 |

| 21       | GND          | Stepper GND                         | GND          | -                 |

| Table 2. Pins description (continued) |

|---------------------------------------|

|---------------------------------------|

1. External components required.

Note: OUT11 and OUT12 are not valid.

DocID027721 Rev 2

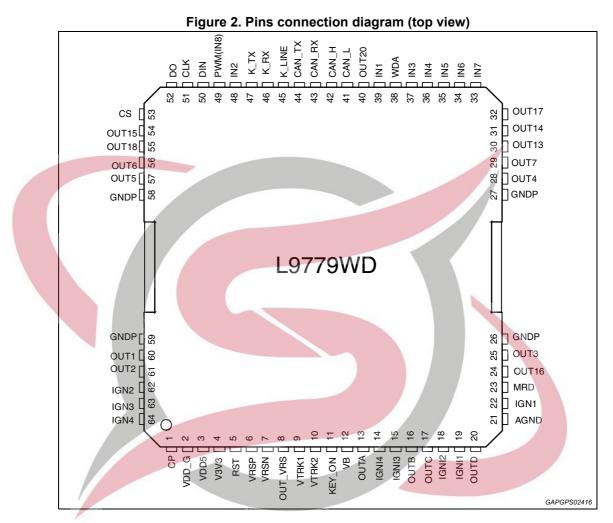

### 4 Application schematic

Figure 3. Application schematic

16/141

DocID027721 Rev 2

#### Absolute maximum ratings 5

#### Warning: Maximum ratings are absolute ratings: exceeding any of these values may cause permanent damage to the integrated circuit

| Pin      | Parameter                            | Condition                                                                                                                             | Value                                           | Unit |

|----------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|

| VB       | DC supply battery power voltage (Vb) | Also without external components                                                                                                      | -0.3 to +40                                     | V    |

| V3V3     | DC logic supply voltage              | -                                                                                                                                     | -0.3 to VDD5, when<br>V3V3 = VDD5 = 19 V max    | V    |

| VTRK1,2  | DC sensors supply voltage            | -                                                                                                                                     | -2 to +40                                       | V    |

| VDD_G    | -                                    | -                                                                                                                                     | -0.3 to VDD5, when<br>VDDG = VDD5 = 19 V max    | V    |

| VDD5     | Voltage pin                          | -                                                                                                                                     | -0.3 to 19                                      | V    |

| СР       | -                                    | -                                                                                                                                     | -0.3 to 40<br>Max ABS = +40 V when<br>VB = 40 V | v    |

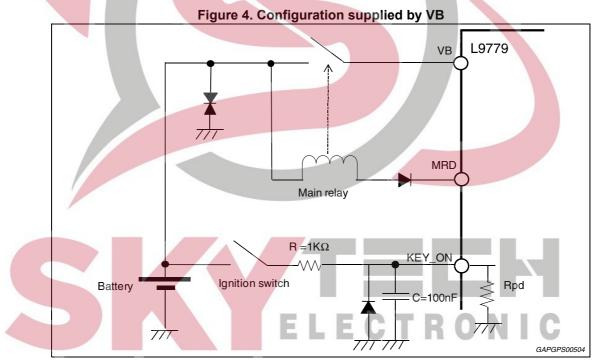

| KEY_ON   | -                                    | Protected with external<br>component (R = 1 k $\Omega$ plus a<br>diode, refer to <i>Figure 4</i> ) for<br>negative pulse (isopulse 1) | -1.2 to +40                                     | v    |

| RST      | -                                    |                                                                                                                                       | -0.3 to +19                                     | V    |

| VRSP     | -                                    | Max current to be limited with<br>external resistors<br>(see Section 6.14.3: Application<br>circuits on page 93)                      | -20 to +20                                      | mA   |

| VRSM     |                                      | Max current to be limited with<br>external resistors<br>(see Section 6.14.3: Application<br>circuits on page 93)                      | -20 to +20                                      | mA   |

| MRD      | -/                                   |                                                                                                                                       | -0.3 to +40                                     | V    |

| OUT1-5   | Low-side output                      |                                                                                                                                       | -1 to +53                                       | V    |

| OUT6-7   | Low-side output                      | -                                                                                                                                     | -1 to +40                                       | V    |

| OUT13-18 | Low-side output                      | -                                                                                                                                     | -1 to +40                                       | V    |

| OUT20    | Low-side output                      | -                                                                                                                                     | -1 to +40                                       |      |

| IGNx     | -                                    | -                                                                                                                                     | -1 to 19                                        | V    |

| Table 3. | Absolute | maximum | ratings |

|----------|----------|---------|---------|

|----------|----------|---------|---------|

DocID027721 Rev 2

| Pin                                                                                             | Parameter          | Condition                                                | Value                                                | Unit |

|-------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------|------------------------------------------------------|------|

| OUTA, OUTB,<br>OUTC, OUTD                                                                       | Half bridge output | With external diode vs<br>ground for negative<br>voltage | -1.0 to VB<br>(–2.0 dynamically for a short<br>time) | v    |

| DO,<br>CAN_RX,K_RX,<br>OUT_VRS                                                                  | -                  | -                                                        | -0.3 to VDD_IO, when<br>DO = VDD_IO = 19 V max       | V    |

| CS, CLK, DIN,<br>IN1, IN2, IN3,<br>IN4, IN5, IN6,<br>IN7, PWM,<br>IGNI1, IGNI2,<br>IGNI3, IGNI4 |                    |                                                          | -0.3 to +19                                          | V    |

| CAN_TX                                                                                          | -                  | -                                                        | -0.3 to +19                                          | V    |

| CAN_H, CAN_L                                                                                    | -                  | -                                                        | -18 to 40                                            | V    |

| K_TX                                                                                            | -                  | -                                                        | -0.3 to +19                                          | V    |

| K_LINE                                                                                          | -                  | -                                                        | -18 to 40                                            | V    |

Table 3. Absolute maximum ratings (continued)

### 5.1 ESD protection

#### Table 4. ESD protection

| Item                             | Condition                                                                                            | Min  | Мах  | Unit |

|----------------------------------|------------------------------------------------------------------------------------------------------|------|------|------|

| All pins                         | Electro static discharge voltage "Charged-device-model – CDM" all pin <sup>(1)</sup>                 | -500 | +500 | V    |

| All pins                         | Electro static discharge voltage "Charged-device-model – CDM"<br>corner pin (1,20,21,32,33,52,53,64) | -750 | +750 | v    |

| All pins                         | ESD voltage HBM respect to GND                                                                       | -2   | +2   | KV   |

| Pins to connector <sup>(2)</sup> | ESD voltage HBM respect to GND                                                                       | -4   | +4   | KV   |

1. Except OUTA, B, C, D ±250 V.

2. Pins are LSa, LSb, LSc, LSd, IGNx, VTRK1-2, CAN\_H, CAN\_L, K\_LINE, OUTA, B, C, D.

Test circuit according to HBM (EIA/JESD22-A114-B) and CDM (EIA/JESD22-C101-C).

ELECTRONIC

DocID027721 Rev 2

### 5.2 Latch-up test

According to JEDEC 78 class 2 level A.

### 5.3 Temperature ranges and thermal data

| Symbol                | Parameter                                                 | Min | Max | Unit |

|-----------------------|-----------------------------------------------------------|-----|-----|------|

| T <sub>amb</sub>      | Operating temperature                                     | -40 | 125 | °C   |

| Тј                    | Continuative operative junction temperature               | -40 | 150 | °C   |

| T <sub>stg</sub>      | Storage temperature                                       | -40 | 150 | °C   |

| R <sub>thj-case</sub> | Thermal resistance junction-to-case                       | -   | 1   | °C/W |

| R <sub>thj-amb</sub>  | Thermal resistance junction-to-ambient <sup>(1)</sup>     | -   | 16  | °C/W |

| Ts                    | Lead temperature during soldering (for a time = 10 s max) | -   | 260 | °C   |

| 1. With 2S2           | 2P+vias PCB.                                              |     |     |      |

#### Table 5. Temperature ranges and thermal data

**Operating range**

5.4

### Table 6. Operating range

| Pins<br>symbol | Battery voltage range                                         | Junction temperature condition | Note           |

|----------------|---------------------------------------------------------------|--------------------------------|----------------|

|                | 4.15 V < Vb < 6 V                                             | -40 < Tj < 40                  | Low battery    |

| VB             | 6 V < Vb = 18 V                                               | -40 < Tj < 150                 | Normal battery |

| VD             | 18 V < Vb = 28 V                                              | -40 < Tj < 40                  | High battery   |

|                | $28 < Vb = 40 V$ , $t_{rise} = 10ms$ , $T_{pulse} = 400 ms$ . | -40 < Tj < 40                  | Load dump      |

### 5.4.1 Low battery

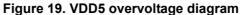

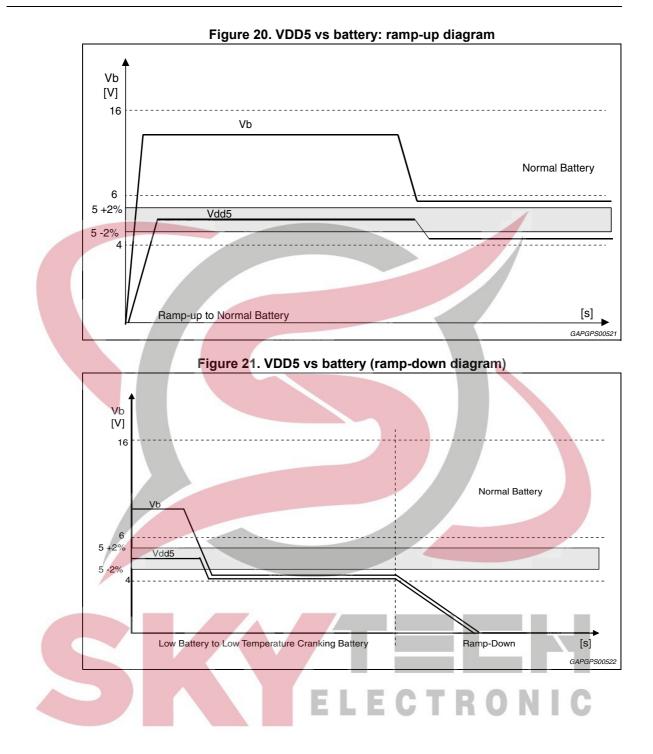

All the functions are guaranteed with degraded parameters. The voltage regulators follow VB in RDSon mode with drop-out depending on load current. V3V3 regulator works as expected assuming VDD5 > 4 V.

### 5.4.2 Normal battery

All the functions and the parameters are guaranteed by testing coverage.

### 5.4.3 High battery

All the functions are guaranteed with degraded parameters.

### 5.4.4 Load dump

The device is switched-off if load dump exceeds battery overvoltage threshold for a time longer than filter time.

DocID027721 Rev 2

### 6 Functional description

### 6.1 Ignition switch, main relay, battery pin

The system has an ignition switch pin KEY\_ON and a pin VB for battery behind the main relay connected at pin MRD.

L9779WD-SPI can also support the configuration where it is permanently supplied by VB; in this case the MRD output can be used to connect the loads to VB.

At pin KEY\_ON there is an external diode for reverse battery protection. An internal Pulldown resistor is provided on the KEY\_ON pin. The external components to be connected to KEY pin are shown in the below schematic.

Internal functions and regulators are supplied by VB; only some basic functions required for startup are supplied from KEY\_ON as described below. Reverse protection for pin VB is done by the main relay. Transient negative voltage at VB may be limited by an external diode if necessary. There is no integrated reverse protection at pin VB.

The pin connected to the battery line can bear the ISO 7637/1 noise pulses without any damage. The VB voltage must be externally limited to +40 V and -0.3 V (with external components as in *Figure 4*). It is suggested the use of a transil.

1. The external components connected to KEY\_ON pin are mandatory in order to protect the device from ISO 7637 pulses.

DocID027721 Rev 2

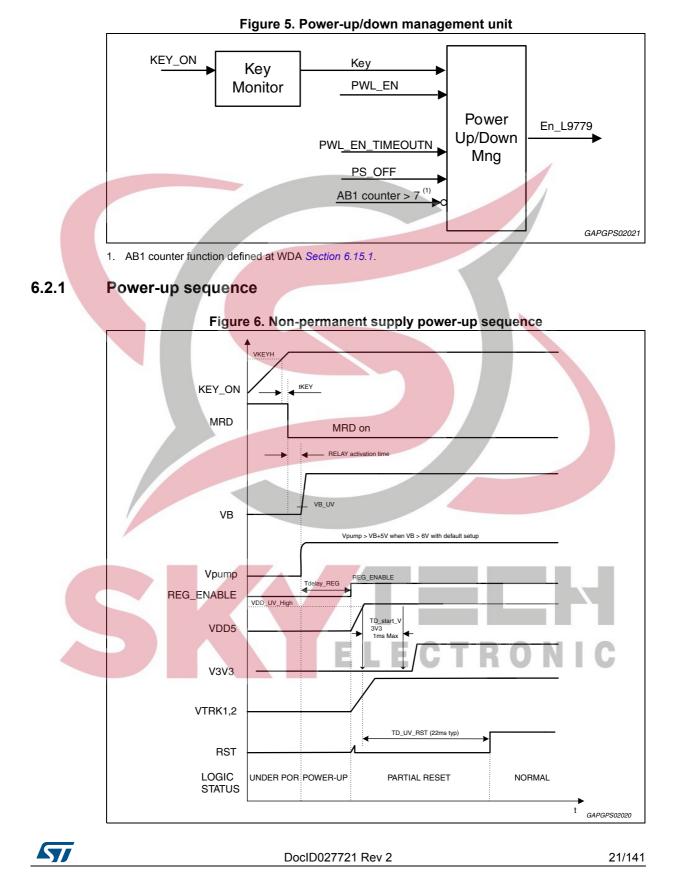

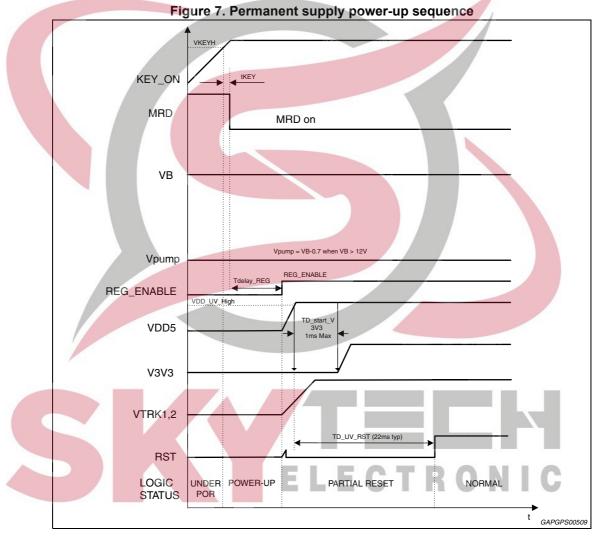

### 6.2 Power-up/down management unit

When the KEY\_ON reaches a sufficient high voltage VKEYH, after a minimum deglitch filter time T\_KEY the system is switched on. First of all the main relay driver is switched on, so the main relay connects VB pin to battery.

Control current into pin KEY\_ON is sufficient for basic functions such as filtering time, control of the main relay output stage, internal oscillator and internal bias currents.

When the voltage at VB exceeds the under voltage-detection threshold for VB (VB\_UV\_H) the internal biasing circuits are activated.

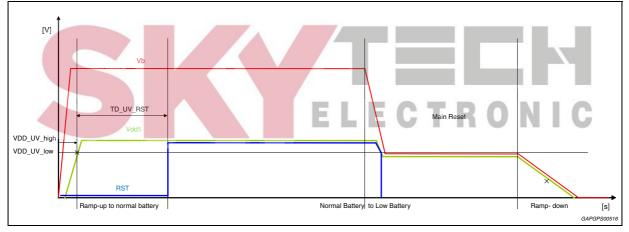

VDD5 regulator is activated Tdelay\_REG seconds later. After VDD5 exceeds the VDD\_UV threshold and with typ. 1.0 ms delay, the V3V3 is activated also. The sensor supplies VTRK1, 2 are turned on together with VDD5.

In the case when VB is always connected, when the KEY\_ON voltage exceeds VKEYH the internal biasing circuits are activated.

VDD5 regulator is activated Tdelay\_REG seconds after the tKEY filter time has expired.

DocID027721 Rev 2

VDD5 regulator is activated Tdelay\_REG seconds later. After VDD5 exceeds the VDD\_UV threshold and with typ. 1.0 ms delay, the V3V3 has activated also. The sensor supplies VTRK1, 2 are turned on together with VDD5.

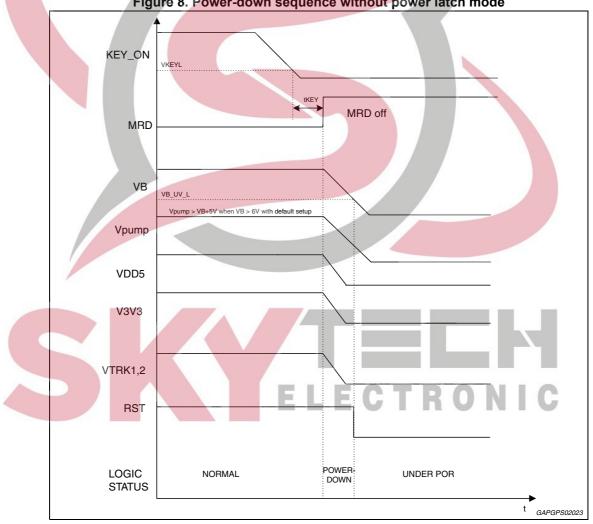

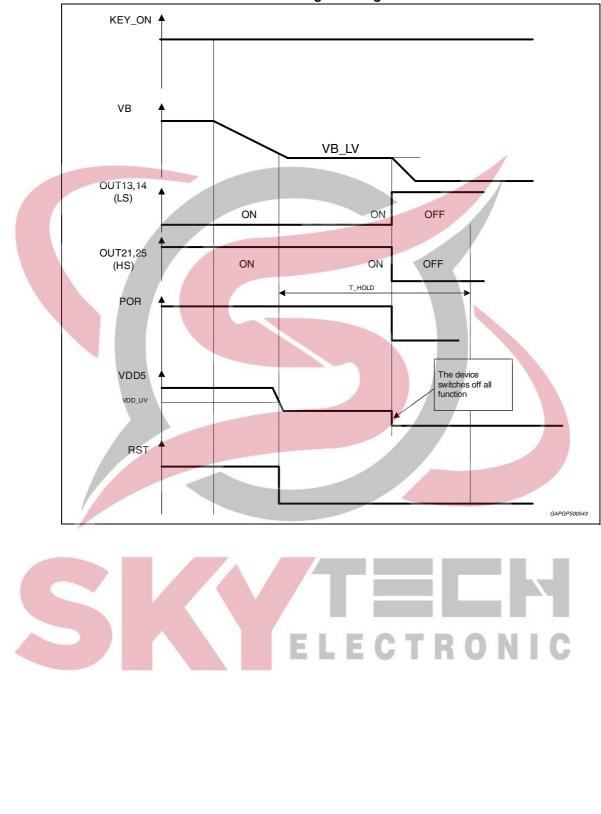

### 6.2.2 Power-down sequence

The system is switched off according to the status of KEY\_ON, VB and power latch mode bit PWL\_EN\_N set by the  $\mu$ C, according to:

En\_L9779 = [(!PWL\_EN\_N AND PWL\_EN\_TIMEOUTN) OR KEY\_ON] AND VB\_UVN.

The KEY\_ON is the status of KEY\_ON pin after deglitch filter time.

En\_L9779 represents the enable signals used by different blocks.

The system will be switched off after a minimum deglitch filter time if the voltage at pin KEY\_ON is below VKEYL and if power latch mode is not active i.e. PWL\_EN\_N =1.

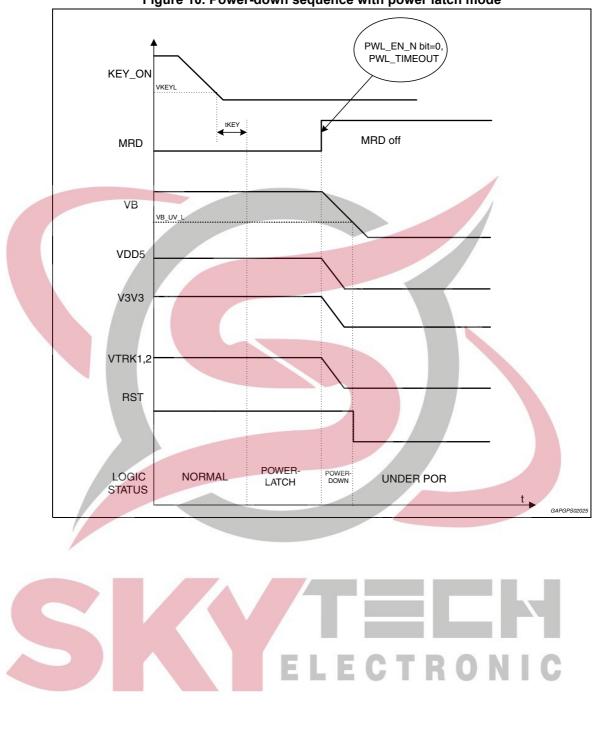

Otherwise, if the power latch mode is active PWL\_EN\_N=0, nothing happens until the power latch mode has finished by the µC writing PWL\_EN\_N=1.

However L9779WD-SPI will wait for a maximum time-out time PWL\_TIMEOUT for PWL\_EN\_N de-assertion after which the system will be forced to switch off. PWL\_TIMEOUT can be enabled and configured by 3 bit PWL\_TIMEOUT\_CONF.

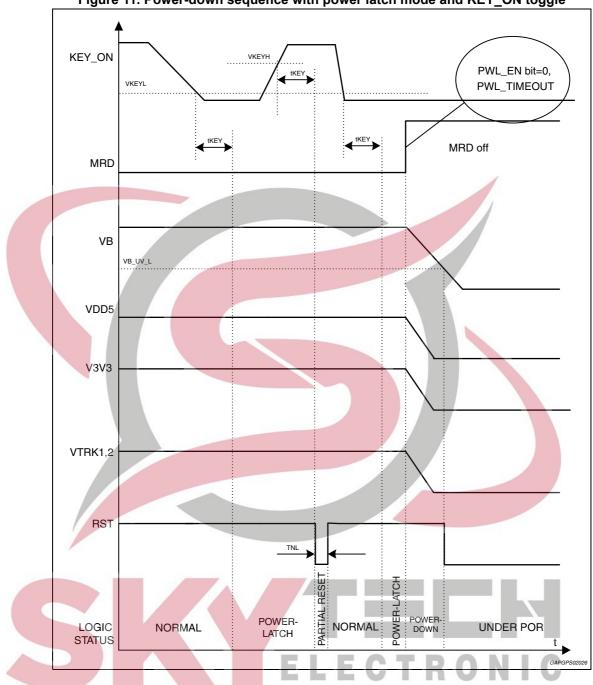

For TNL description see Smart reset circuit description.

The status of KEY\_ON can be read through the bit KEY\_ON\_STATUS. After tKEY filter time the status of KEY\_ON can be read through the bit KEY\_ON\_FLT also.

All the supply outputs shall be switched-off simultaneously. If the supplied devices have particular sequencing requirements, external diodes or clamping devices will be used.

During power down, whether the regulators are switched off at the same time as the main relay output or not is decided via the <PSOFF> bit.

- <PSOFF>='0' (default): simultaneous switching-off the regulators with the main-relay driver MRD

- <PSOFF>='1': regulators remain active when the main relay driver MRD will be switched off

With this function it is possible to detect a stuck main relay. If conditions to switch off are satisfied when <PSOFE>='1', the MRD is switched off while the voltage regulators continue to operate as long as no under voltage is detected at VB. The RST pin is not asserted till VDD\_UV. The  $\mu$ C measures the time passed since shutdown. If a certain time is exceeded, then a stuck main relay is detected and this fault is stored in the  $\mu$ C (not in the L9779WD-SPI). After this the  $\mu$ C turns off the voltage regulators by setting the bit <PSOFE> to '0' (reset state). With a stuck main relay the voltage at pin VB remains present at battery

level with a current consumption of ILeak.

Secure Engine Off function is that the engine can be directly switched off by the key-switch via a hardware path and without the help or interference of software or  $\mu$ C.

Whenever the KEY\_ON signal goes low the output stages mentioned in the following pages are disabled, no matter what other conditions (like e.g. "power-latch") are.

In no power latch/no SEO mode the key-switch has direct shut-off access to the injector stages (OUT1-4) and to the starter relay drivers (OUT13 and OUT14).

DocID027721 Rev 2

An additional feature for the starter delay drivers is that the starters are only shut-off after the time delay THOLD if the SEO condition is still active.

The ignition stages are not affected by the SEO signal. This is different from the WDA signal which additionally switches off the ignition stages.

To avoid misunderstandings one must be aware that the SEO function has nothing to do with the WDA function and is not a part of the WDA module. The SEO function is related to the key switch, not to the WDA function. The SEO function adds an additional safety procedure for switching off.

Other functions than the injector stages and the starter relay drivers are not affected or influenced by the SEO signal.

With the falling edge of KEY ON a timer is started which disables the mentioned power stages after 200 ms to 250 ms (typ. 225 ms). The timer is clocked by an internal oscillator. The timer does not depend on any  $\mu$ C clock or function. The  $\mu$ C still has control on switching on/off drivers during SEO time. This function is configured by CONFIG REG6 register.

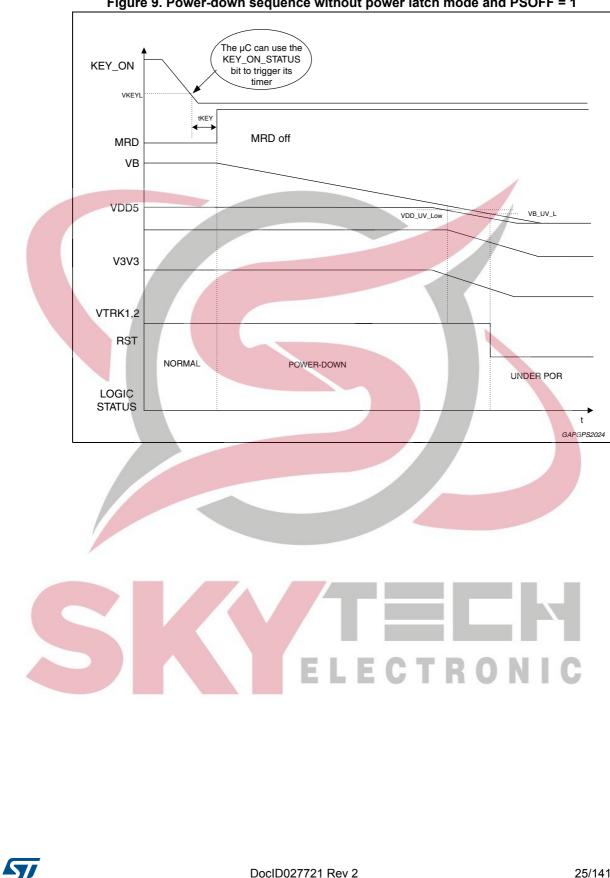

Figure 8. Power-down sequence without power latch mode

24/141

DocID027721 Rev 2

Figure 9. Power-down sequence without power latch mode and PSOFF = 1

Figure 10. Power-down sequence with power latch mode

DocID027721 Rev 2

Figure 11. Power-down sequence with power latch mode and KEY\_ON toggle

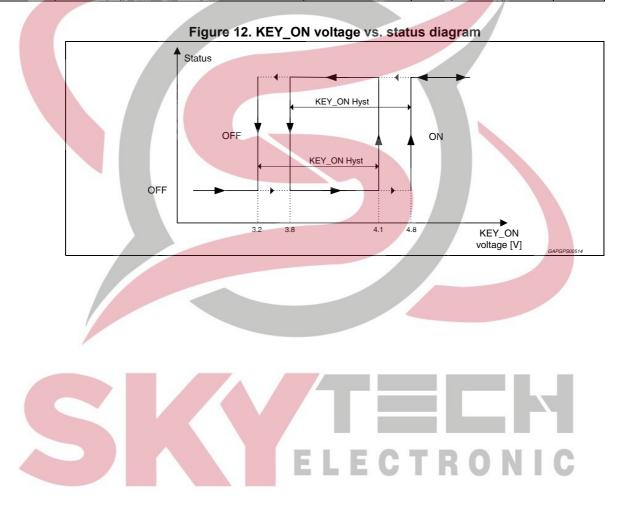

| Pin    | Symbol           | Parameter                                                         | Test condition                 | Min  | Тур | Max | Unit |

|--------|------------------|-------------------------------------------------------------------|--------------------------------|------|-----|-----|------|

|        | VKEYL            | Input threshold low voltage                                       |                                | 3.2  | 3.5 | 3.8 | V    |

|        | VKEYH            | Input threshold high voltage                                      | VB = 0 to 19 V                 | 4.15 | 4.5 | 4.8 | V    |

|        | VKEYHYS          | Input voltage hysteresis                                          |                                | 0.5  | 1   | 1.5 | V    |

| KEY_ON | I_KEY            | Input current                                                     | VB = 0 to 19 V<br>KEY_ON = 5 V | -    | -   | 550 | μA   |

|        | t <sub>KEY</sub> | Filter time for switching on/off                                  | VB = 0 to 19 V                 | 7.5  | 16  | 24  | ms   |

|        | Rpd              | Internal pull down resistor - NOT<br>tested - Guarantee by design | KEY_ON = 5 V                   | 150  | -   | 400 | kΩ   |

Table 7. KEY\_ON pin electrical characteristics

### 6.3 Smart reset circuit

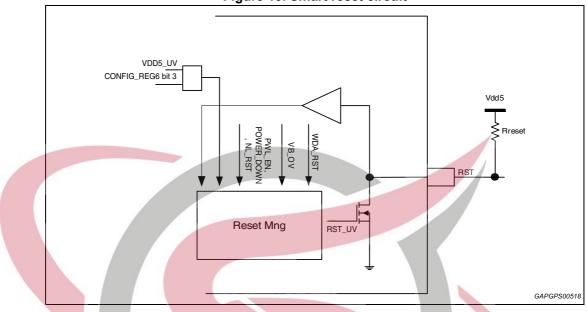

Figure 13. Smart reset circuit

### 6.3.1 Smart reset circuit functionality description

The RST pin is an input/output active when low. As output pin the Smart Reset circuit takes into account several events of the device in order to generate the proper reset signal at RST pin for the microcontroller and for a portion of the internal logic as well. As input pin RST when driven low by external source for more than Trst\_flt, it is used to reset the same portion of logic of the device.

The sources of reset are:

- VDD5 under voltage it can be disabled by SPI CONFIG\_REG6 bit3 = high, default is low i.e. enabled

- Power down

- Power latch, KEY\_ON

- VB overvoltage

- WDA\_RST, query and answer watchdog reset

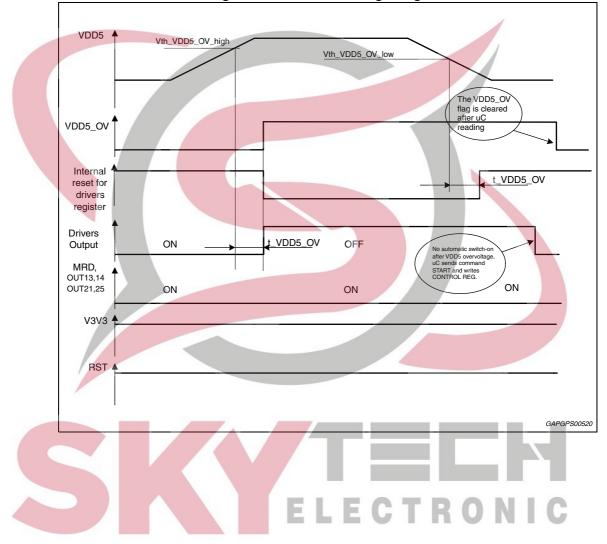

Smart reset circuit generates RST signal monitoring the VDD5 according to the graph shown below: when VDD5 falls below VDD\_UV\_LOW threshold for a time longer than TfUV\_reset Smart Reset circuit asserts a RST signal (driven low) and the flag CRK\_RST is latched and resets every Read Diag operation. When VDD5 recovers to a voltage greater than VDD\_UV\_HIGH RST pin is deasserted after Td\_UV\_rst. The RST pin is also asserted at the first power-on phase when the KEY\_ON pin goes from low to high, as a consequence of the VDD5 absence.

Smart reset circuit generates an RST signal at power down independently of filtering time and VDD5 voltage level. During power latch mode if NL\_RST bit is set and KEY\_ON signal goes low to high again (before microcontroller was able to write PWL\_EN\_N=0), RST\_PIN is asserted for time TNL.

DocID027721 Rev 2

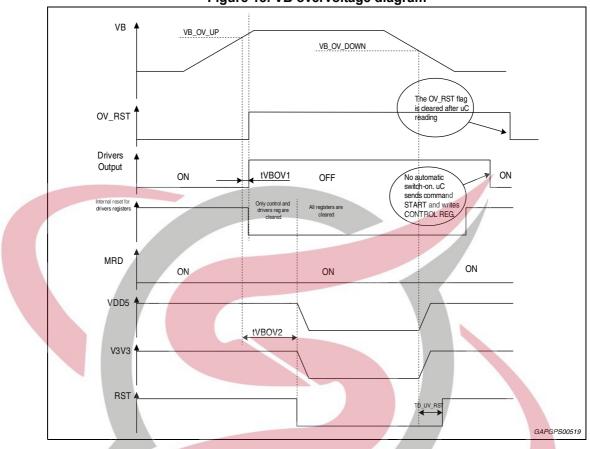

Smart reset circuit monitors VB over voltage and generates RST signal if the over voltage lasts more than tVBOV2. When over voltage lasts more than tVBOV1 and less than tVBOV2, RST is not asserted, but all drivers are switched off without losing any configuration. In both cases the flag VB\_OV is latched and resets every Read Diag operation.

When RST is asserted to reset the  $\mu$ C, also all logic will be reset except logic involved in reset management, power up management, and power down management units. As a consequence all flags are cleared except those set by the smart reset unit, all drivers are disabled except the low battery drivers, all configuration registers are cleared and OUT\_DIS bit goes to 1. A more detailed description of the module under reset can be found in the next table. The table summaries also relations with other conditions that switch off drivers and regulator.

|                                                                                                                                                                                                                                                                                                                                        | 1                           | Table 0. II                                                                                                      | iternal reset                                                                                                                                  |                                                  |                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------|

| Event                                                                                                                                                                                                                                                                                                                                  | RST<br>pin<br>driven<br>low | Logic under reset                                                                                                | Logic not reset                                                                                                                                | Power-up/down<br>manager output                  | Information<br>FLAG |

| Power down                                                                                                                                                                                                                                                                                                                             | Yes                         | Internal registers<br>Interfaces drivers<br>LB interfaces drivers<br>LB internal registers<br>CAN & K-LINE & VRS | Smart reset function<br>Power-up/down<br>manager                                                                                               | MRD=OFF<br>VDD5=OFF<br>V3V3=OFF<br>VTRACK1,2=OFF | N/A                 |

| Power latch<br>+KEY_ON rising<br>edge                                                                                                                                                                                                                                                                                                  | Yes<br>For<br>TNL           | Internal registers<br>Interfaces drivers<br>LB interfaces drivers<br>LB internal registers<br>CAN & K-LINE & VRS | Smart reset function<br>Power-up/down<br>manager                                                                                               | MRD=ON<br>VDD5=ON<br>V3V3=ON<br>VTRACK1,2=ON     | TNL_RST             |

| VDD5 under<br>voltage<br>t <thold< td=""><td>Yes</td><td>Internal registers<br/>Interfaces drivers<br/>CAN &amp; K-LINE &amp; VRS</td><td>LB interfaces drivers<br/>LB internal registers<br/>Smart reset function<br/>Power-up/down<br/>manager</td><td>MRD=ON<br/>VDD5=ON<br/>V3V3=ON<br/>VTRACK1,2=ON</td><td>CRK_RST</td></thold<> | Yes                         | Internal registers<br>Interfaces drivers<br>CAN & K-LINE & VRS                                                   | LB interfaces drivers<br>LB internal registers<br>Smart reset function<br>Power-up/down<br>manager                                             | MRD=ON<br>VDD5=ON<br>V3V3=ON<br>VTRACK1,2=ON     | CRK_RST             |

| VDD5 under<br>voltage<br>t>THOLD                                                                                                                                                                                                                                                                                                       | Yes                         | Internal registers<br>Interfaces drivers<br>LB interfaces drivers<br>LB internal registers<br>CAN & K-LINE & VRS | Smart reset function<br>Power-up/down<br>manager                                                                                               | MRD=ON<br>VDD5=ON<br>V3V3=ON<br>VTRACK1,2=ON     | VDD5UV_<br>RST      |

| VDD5 over voltage                                                                                                                                                                                                                                                                                                                      | No                          | Interfaces drivers                                                                                               | Internal registers<br>LB interfaces drivers<br>LB internal registers<br>CAN & K-LINE & VRS<br>Smart reset function<br>Power-up/down<br>manager | MRD=ON<br>VDD5=ON<br>V3V3=ON<br>VTRACK1,2=ON     | VDD5_OV             |

|       | ~  | 1 4 1    |       |

|-------|----|----------|-------|

| lable | Χ. | Internal | reset |

30/141

DocID027721 Rev 2

| Event                                                                                                                                                                                                                                                                                                | RST<br>pin<br>driven<br>low | Logic under reset                                                                                                | Logic not reset                                                                                                       | Power-up/down<br>manager output                 | Information<br>FLAG |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|--|--|

| VB over voltage<br>t <sub>TBOV1</sub> <t<t<sub>TBOV2</t<t<sub>                                                                                                                                                                                                                                       | No                          | Interfaces drivers<br>LB interfaces drivers                                                                      | Internal registers<br>LB internal registers<br>CAN & K-LINE & VRS<br>Smart reset function<br>Power-up/down<br>manager | MRD=ON<br>VDD5=ON<br>V3V3=ON<br>VTRACK1,2=ON    | OV_RST              |  |  |

| VB over voltage<br>t>t <sub>TBOV2</sub>                                                                                                                                                                                                                                                              | Yes                         | Internal registers<br>Interfaces drivers<br>LB interfaces drivers<br>LB internal registers<br>CAN & K-LINE & VRS | Smart reset function<br>Power-up/down<br>manager                                                                      | MRD=ON<br>VDD5=OFF<br>V3V3=OFF<br>VTRACK1,2=OFF | OV_RST              |  |  |

| RST driven low<br>externally<br>t <thold< td=""><td>Yes</td><td>Internal registers<br/>Interfaces drivers<br/>CAN &amp; K-LINE &amp; VRS</td><td>LB interfaces drivers<br/>LB internal registers<br/>Smart reset function<br/>Power-up/down<br/>manager</td><td>Keep state</td><td>N/A</td></thold<> | Yes                         | Internal registers<br>Interfaces drivers<br>CAN & K-LINE & VRS                                                   | LB interfaces drivers<br>LB internal registers<br>Smart reset function<br>Power-up/down<br>manager                    | Keep state                                      | N/A                 |  |  |

| RST driven low<br>externally<br>t>THOLD                                                                                                                                                                                                                                                              | Yes                         | Internal registers<br>Interfaces drivers<br>LB interfaces drivers<br>LB internal registers<br>CAN & K-LINE & VRS | Smart reset function<br>Power-up/down<br>manager                                                                      | Keep state                                      | N/A                 |  |  |

| Software reset sent<br>by the µC through<br>SPI                                                                                                                                                                                                                                                      | No                          | Internal registers<br>Interfaces drivers<br>LB interfaces drivers<br>LB internal registers<br>CAN & K-LINE & VRS | Smart reset function<br>Power-up/down<br>manager                                                                      | MRD=ON<br>VDD5=ON<br>V3V3=ON<br>VTRACK1,2=ON    | N/A                 |  |  |

| Legend:                                                                                                                                                                                                                                                                                              |                             |                                                                                                                  |                                                                                                                       |                                                 |                     |  |  |

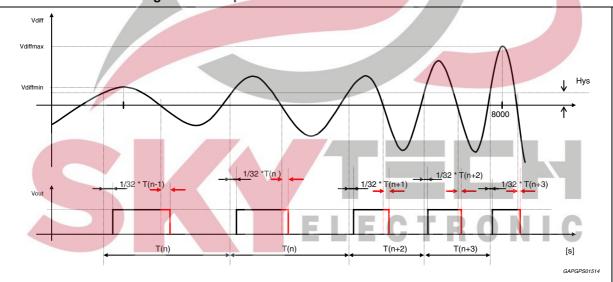

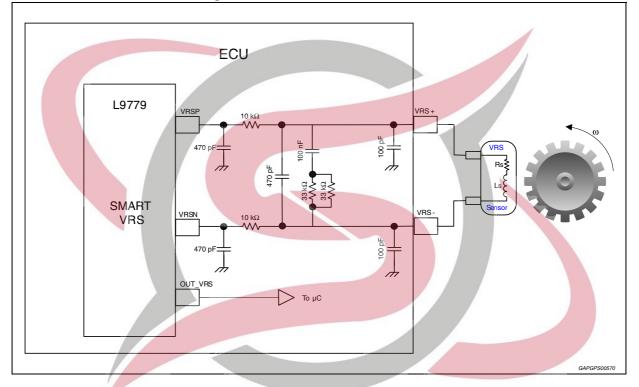

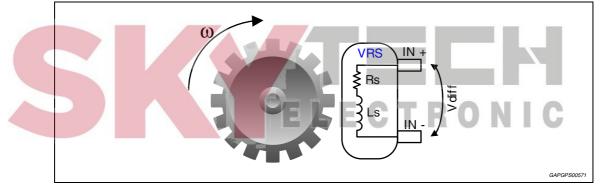

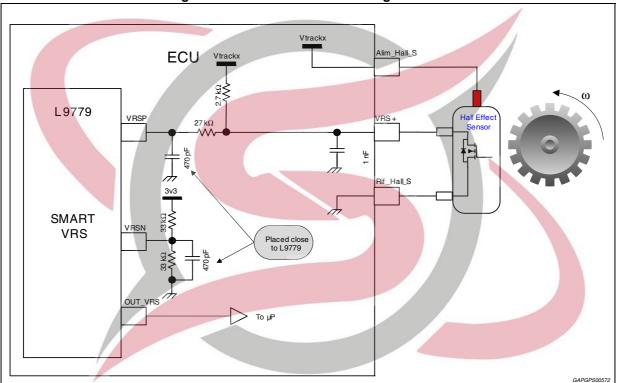

| Internal registers = configuration registers CTRONIC                                                                                                                                                                                                                                                 |                             |                                                                                                                  |                                                                                                                       |                                                 |                     |  |  |